Filed Dec. 23, 1957

16 Sheets-Sheet 1

INVENTORS

MAURICE PAPO

ATTORNEY

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

May 31, 1960

## E. ESTREMS ET AL

2,939,120

CONTROLS FOR MEMORY DEVICES

Filed Dec. 23, 1957

FIG\_2h\_

Filed Dec. 23, 1957

Filed Dec. 23, 1957

May 31, 1960

## E. ESTREMS ET AL

2,939,120

CONTROLS FOR MEMORY DEVICES

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

16 Sheets-Sheet 14

FIG.8.

Filed Dec. 23, 1957

May 31, 1960

## E. ESTREMS ET AL

2,939,120

CONTROLS FOR MEMORY DEVICES

Filed Dec. 23, 1957

|      | FIG. | FIG. | FIG. | FIG. | FIG. |

|------|------|------|------|------|------|

|      | 2h.  | 2 i. | 2j-  | 2k   | 2g.  |

| FIG. | FIG. | FIG. | FIG. | FIG. | FIG. |

| 2a.  | 2b.  | 2c.  | 2d.  | 2e.  | 2f.  |

FIG\_14.

FIG\_ 13\_

#### 2,939,120

#### CONTROLS FOR MEMORY DEVICES

Eugeni Estrems, Saint Mande, and Maurice Papo, Parls, France, assignors to International Business Machines Corporation, New York, N.Y., a corporation of New York

> Filed Dec. 23, 1957, Ser. No. 704,780 16 Claims. (Cl. 340—174)

This invention relates to improvements in computing 15 machines and particularly to improvements in controls for memory elements.

One embodiment of the present invention utilizes two scanning chains or rings associated with an array of memory elements such that data read from one field of 20 the array may be transferred into another field of the same memory array or another memory array character by character.

An apparatus operating in this manner with the ability to split a memory array into an arbitrary number of fields 25 is shown and described in the copending application to E. Estrems, Serial No. 710,312 filed January 21, 1958.

The apparatus of the above-mentioned copending application is adapted to circuits of some simplicity, but at the price of relatively important time losses and substantially intricate connections. For example, it is necessary to search for the memory field to which access is desired. That can be done through a systematic scanning of all the locations in the memory and a search for field beginning coincidence, but it is quite obvious that time sused during this search, extends the calculation time correspondingly. It is also necessary to determine for each memory field, the location corresponding to the lowest ordered position and that corresponding to the highest ordered position of a field, which requires a corresponding number of connections.

Such a mode of definition of memory fields is acceptable if constant length fields are to be processed. In such a case, it is necessary to define for each field its beginning and its end.

In many applications, such as those involving punched cards, the lengths and positions of the several fields are fixed. In such cases the memory array may be split in several fields, such that all the fields are contiguous to each other, and according to the present invention, any connection defining the beginning of a field may be used for defining the end of the preceding field and conversely any connection defining the end of a field may be used for defining the beginning of the next field.

If each location in a storage array is arbitrarily assigned a number to form a continuous sequence from 1 to N, a field is constituted by a series of numbers of decreasing order and that to the locations of a field there corresponds a series of numbers, decrease-wise for example with respect to the numbering order. Thus, a connection corresponding to any location of order P in the memory (and subsequently defining this location without ambiguity), may serve the purpose of defining order locations P+1 or P-1. If this connection corresponds to the highest weight location in a field, and if scanning is performed in the order inverse to numbering, this connection indicates that the end of this field has been reached, and that scanning must be interrupted. Reciprocally, if this connection corresponds to the lowest weight location in a field, it may serve the purpose of starting an operation so as to set scanning in action. In that 70case, the next connection met indicates that the end of

2

the field has been reached, and again scanning must be interrupted.

A primary object of this invention is to provide an improved process of splitting a memory in an arbitrary number of fields. In the present embodiment of the invention these fields are defined by a single connection, this connection corresponding to a selection either of the lowest order or the highest order of said field, circuits being so arranged that this sole connection may serve, at the same time, for defining the beginning of a field and the end of the immediate contiguous field.

Another object of the present invention is to provide improved means for controlling scanning chains whereby a direct start of said chains in a selectively specified location may be had. This location may correspond to the lowest order in the split fields controlled by said chains.

Another object of this invention is to provide an improved circuit arrangement, and a new mode of controlling emitting and receiving memories such that scanning and read-out operations in the emitting memory, and scanning and write operations in the receiving memory are limited to memory fields which have been selected, and particularly are interrupted by the connection used for defining the contiguous split field.

Another object of this invention is to provide improved control and selection for the split fields. Contiguous units capable of receiving control and definition connections of the split fields may be used. These contiguous units are connected to each other through circuits so arranged that any connection may at the same time serve the purpose of the definition connection for the beginning of a split field A and for the end of another split field B, if for example, it is located immediately on the left of the connection which defines field B and if besides, it corresponds to a memory location of an order number lower than the order number of the memory location where field B begins.

Another object of this invention is to provide improved control circuits for a program unit.

Another object is to provide an improved program unit adapted to set a scanning chain in the lowest order location in the memory field controlled for read-out or write.

Another object is to provide an improved program unit adapted to control read-out or write of information data and operations performed on these data.

Another object of this invention is to provide an improved program unit adapted to search, on occasion, for a sign if said sign is not in a location specially provided for the purpose.

Another object is to provide an improved program unit adapted to replace the obtained number by its complement if the performed operation provides the complement for the desired result.

Another object is to provide a program unit with improved advancing controls responsive to the completion of an operation.

Another object is to provide improved program branching in response to calculated data,

Other objects of the invention will be pointed out in the following description and claims and illustrated in the accompanying drawings, which disclose, by way of examples, the principle of the invention and the best mode, which has been contemplated, of applying that principle.

In the drawings:

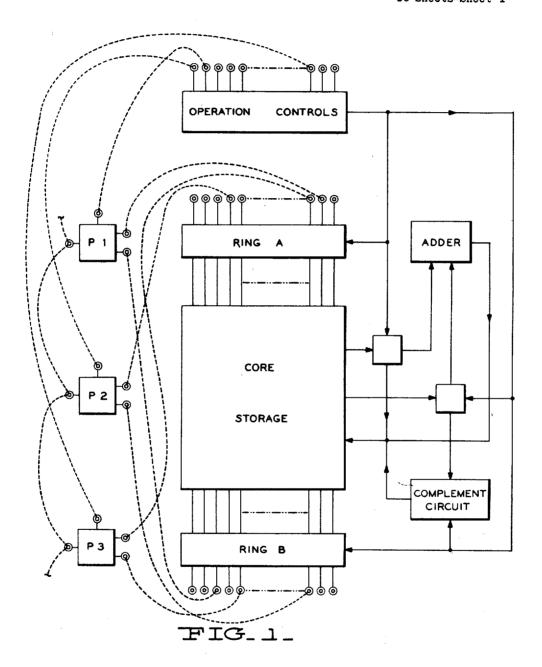

Fig. 1 is a general block diagram of a data processing machine embodying the present invention.

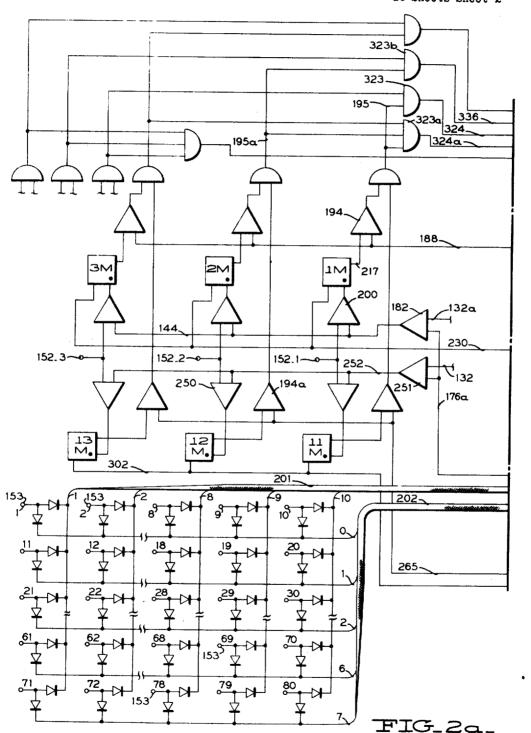

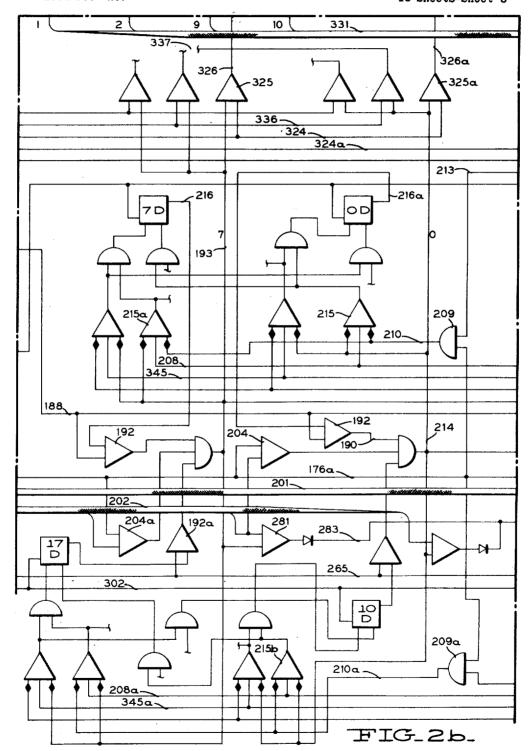

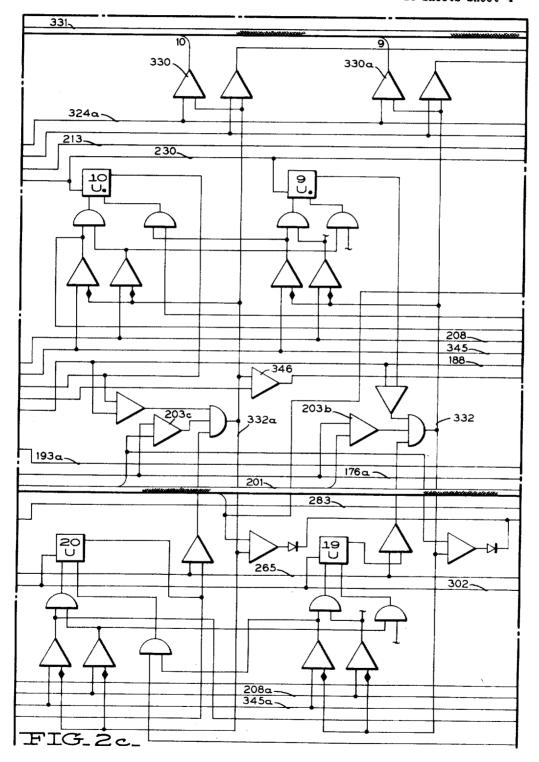

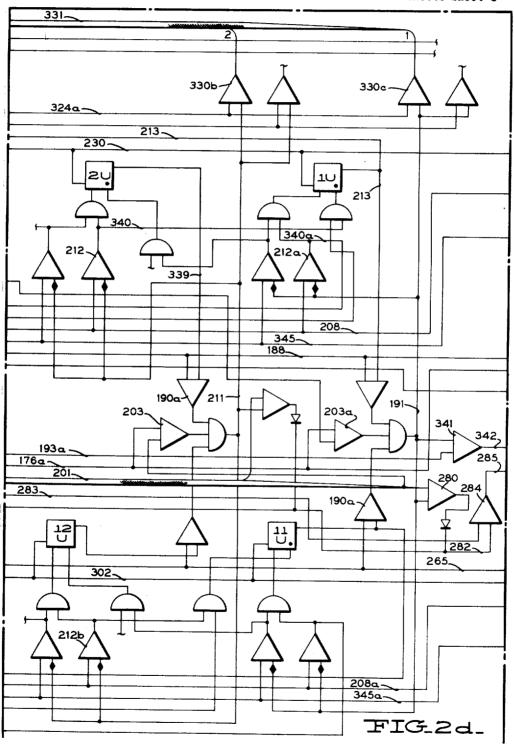

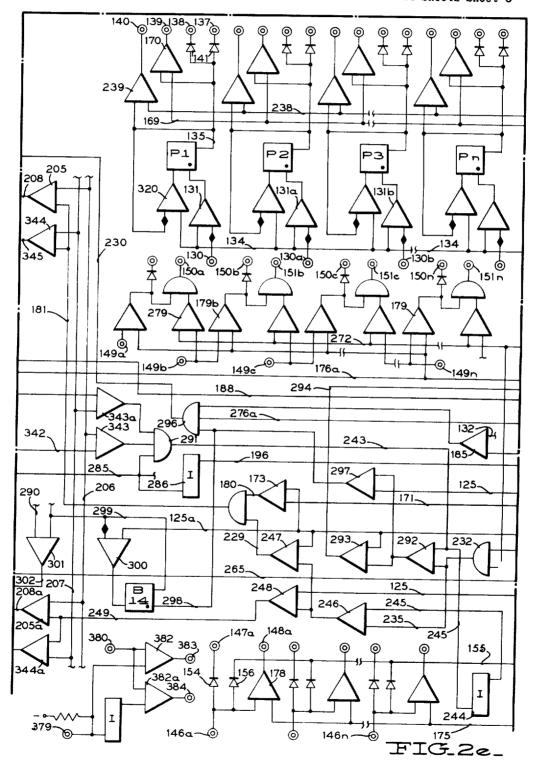

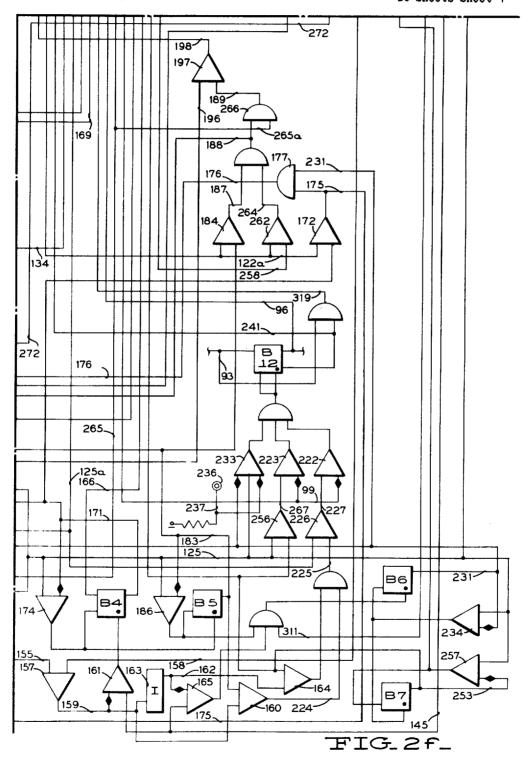

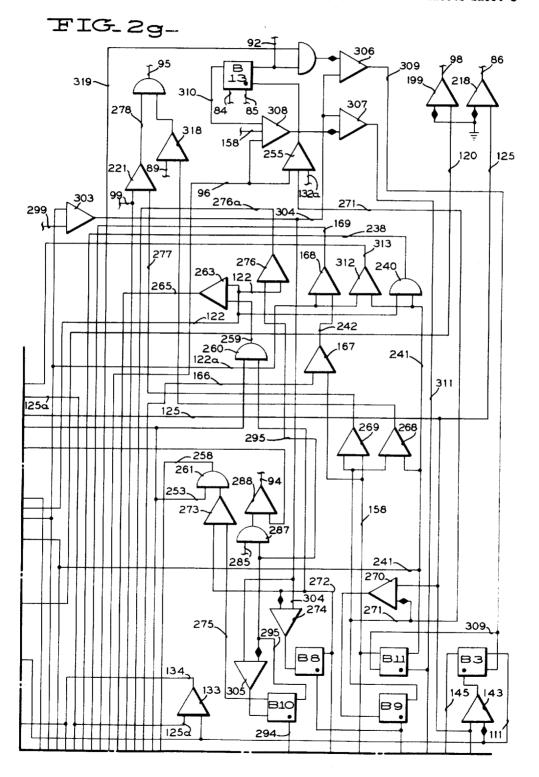

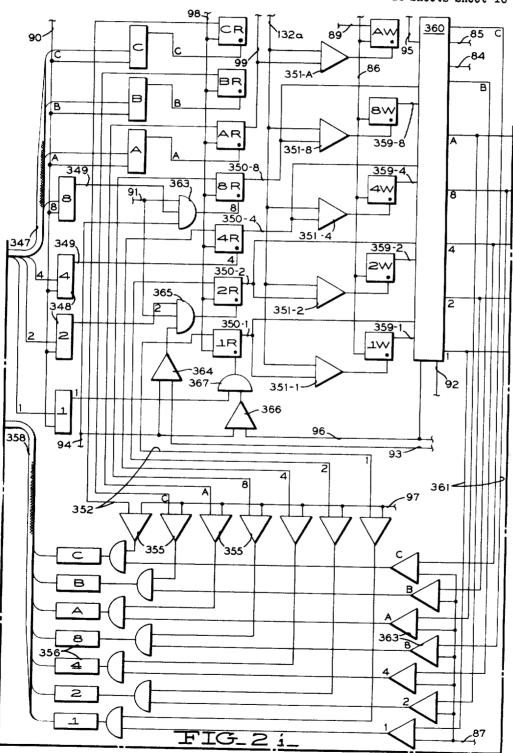

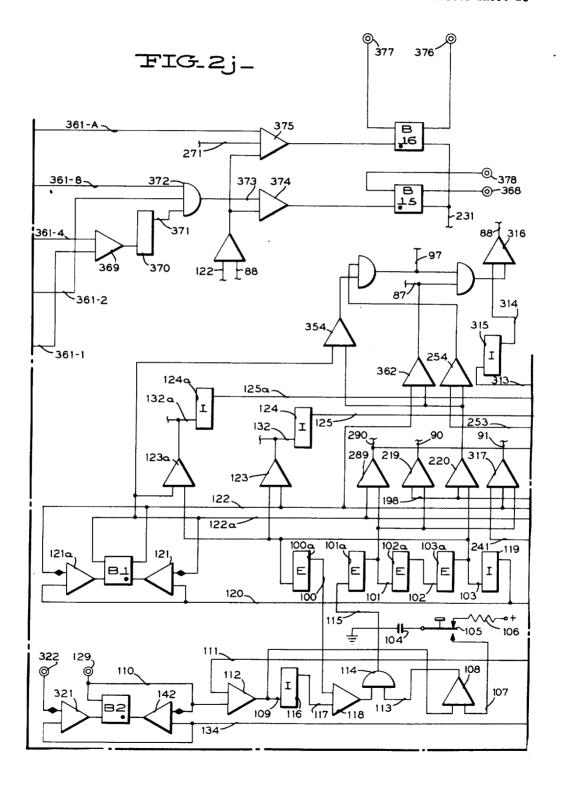

Figs. 2a through 2k taken together are a more detailed block diagram of the machine of Fig. 1.

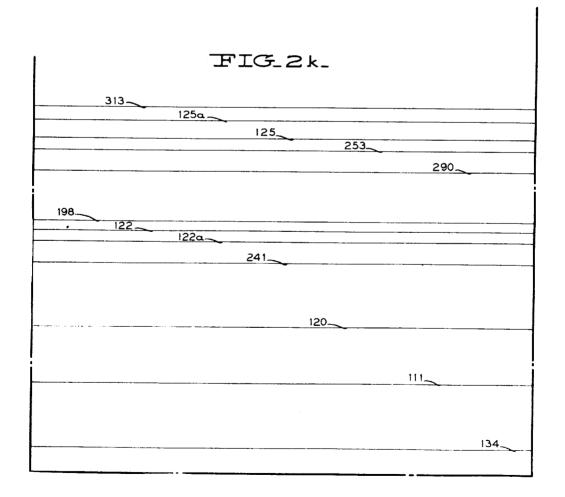

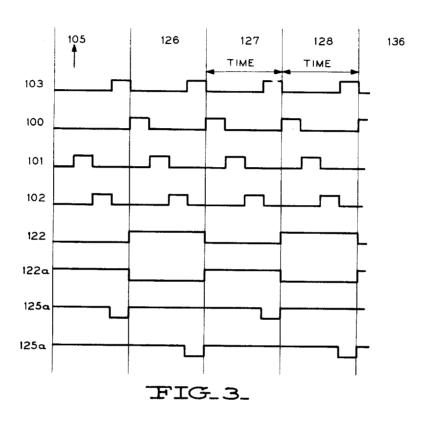

Fig. 3 shows the sequence order in time of certain pulses with the numerals at the left indicating also the lines of Figs. 2a through 2k on which the pulses appear,

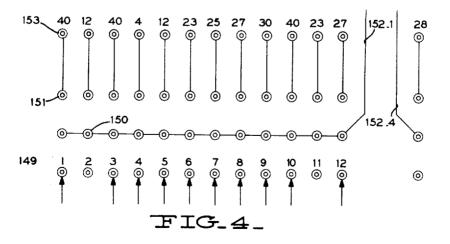

Fig. 4 is an example of some of the control panel hubs used in the present machine.

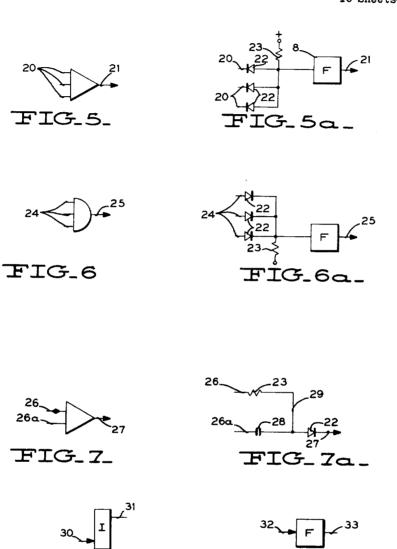

Figs. 5 through 12 show different basic circuits and the symbolical form in which these circuits are shown in Figs. 2a through 2k.

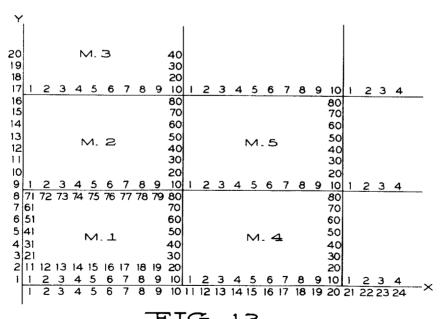

Fig. 13 shows how the various memories may be juxtaposed.

Fig. 14 shows how Figs. 2a through 2k should be placed together.

Referring first to Fig. 1, there is shown a general block 10 diagram of a data processing machine according to the present invention. Only that part of the machine concerned with the present invention is shown. Only program steps P1, P2 and P3 are indicated although a machine would normally include many more. A program 15 step such as P2 may be considered one stage of a ring. The several stages of a ring so formed are connected together with pluggable connectors in order that the steps may be energized in any sequence desired. A core storage array is shown addressed by rings A and B. 20 Rings A and B are under control of the program steps and independently addressed the core storage array. For example, program step P2 has a plugged connection to The plugged connection, a single wire to ring A, sets ring A in the corresponding position to thus ad- 25 conversely. A circuit similar to that shown in Fig. 9 dress core storage. This connection also serves the function of stopping the advance of ring A when ring A advances to this position as a result of having been started by program step P3, for example. The data addressed in this manner by rings A and B are read out 30 from storage, that addressed by ring A being interlaced with that addressed by ring B, to an adder, to a complementing circuit or back into storage. Data addressed by ring A may be transferred to storage positions addressed by ring B or data may be addressed by both 35 rings and fed through the complementing circuit and back to the original location. These and other data flows and controls are described in detail later with reference to Figs. 2a through 2k.

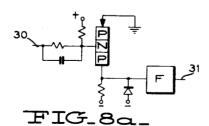

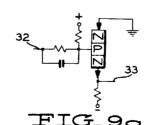

Fig. 9a is the symbolic diagram showing of a power 40 circuit as shown schematically in Fig. 9. The purpose of this circuit is to amplify in power the signal appearing on line 32 and deliver it over line 33. The use of this circuit is to allow a simultaneous feeding of several circuits or the feeding of a common output with pulses 45 from several different sources. As a general rule, the circuit in Fig. 9 is not shown. It is considered as being incorporated in some of the circuits in Figs. 5, 6, 8, 10, 11 and 12.

Input lines 20 receive a voltage normally negative which, in certain conditions may become positive. In the first case, output line 21 receives a negative voltage due to the fact that diodes 22 enable the current to flow, and that a relatively significant voltage drop occurs across resistor 23. This is true even when one only of wires 20 is negative. On the other hand, if all wires 20 are traversed simultaneously by a positive voltage, no current flows through diodes 22 so that across resistor 23 there is only the leak current flowing through line 21. The corresponding voltage drop being relatively low, potential in line 21 takes a positive value. This positive value of potential characterizes the existence of a coincidence between positive input pulses. The latter may be in any number (2, 3, etc. according to the requirement).

The circuit of Fig. 5a is represented symbolically as shown in Fig. 5. According to the use, the output is taken directly or through a circuit similar to that shown

Fig. 6 shows the symbolic form of the OR circuit 70 shown schematically in Fig. 6a. Line 25 has a voltage normally negative which becomes positive when one of input lines 24 is positive. The circuit in Fig. 6a may be recognized in Figs. 2a through 2k by its configuration, and is thus not generally referenced. According to the 75 part. It is possible also to have a control 45 connected

use, the output may be taken directly or through a circuit similar to that shown in Fig. 9.

Fig. 7 is the symbolic form in which the circuit of Fig. 7a is shown. The latter is a coincidence circuit meant for transferring short duration positive pulses required for the control of triggers such as shown in Fig. 11. Inputs 26 and 26a (Fig. 7a) normally are negative and positive respectively and are adapted for receiving positive pulses and negative pulses, respectively. As long as input 26 is negative, pulses directed into input 26a remain of no effect due to line 29 which then has a negative potential and to diode 22 which blocks pulse transferring. On the other hand, when input 26 has a positive voltage, potential in line 29 also takes a positive value, thus permitting the transmission of all the positive pulses from input 26a. That is the case every time the potential in line 26a comes back to a positive value from a negative value. Capacitor 28 then generates a short duration positive pulse which causes potential in line 29 to increase momentarily. Circuits are so arranged that diode 22 allows the current to pass.

Fig. 8 is the symbolic form in which the schematic circuit of Fig. 8a is shown. The latter is an inverter. Output 31 is positive every time the input is negative and may be included in the output.

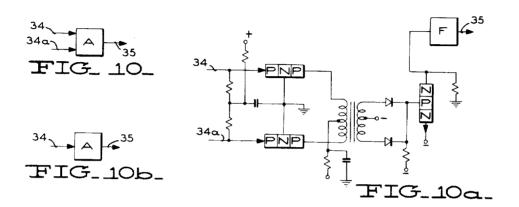

Fig. 10 is a symbolic showing of one of the amplification circuits used in conjunction with magnetic core memories. E.M.F., induced during magnetization reversal is applied between inputs 34 and 34a. A positive pulse then is available at output 35. The circuit is shown in the symbolic form in Figs. 2a through 2k. In Fig. 10b, only one input is shown, the other is assumed to be returned to a fixed potential. A circuit similar to that shown in Fig. 9 may be inserted in the output.

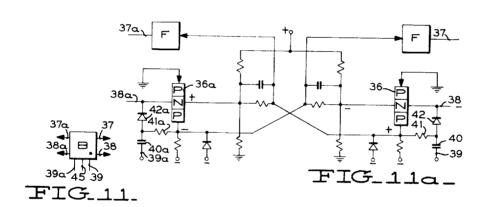

Fig. 11 is a schematic showing of a transistorized trigger. Such a circuit has particularly been described in applicant's copending application Serial No. 643,369 filed March 1, 1957. A first stable state of this circuit corresponds to a conduction achieved for example through transistor 36. In this case, output 37 takes a negative voltage while output 37a has a positive voltage. state of the trigger may be switched by a positive pulse applied to input 38. A positive pulse applied to input 38a is of no effect. The switching pulse may be from a circuit of the type represented in Figs. 7 and 7a.

The state of the trigger (Fig. 11a) may be switched by the application of a positive voltage to line 39. voltage affects the circuit formed by capacitor 40, re-Fig. 5a shows in schematic form a coincidence circuit. 50 sistor 41 and diode 42, which circuit is an assembly formed by the component elements of Fig. 7a. It should be noted particularly that one of the ends of resistor 41 is integral with output 37a, which now is assumed to have a positive voltage. A positive voltage directed 55 into line 39a is of no effect due to the end of resistor 41a which is connected to line 37 now assumed to have a negative voltage. Generally speaking, it is possible to direct several pulses into lines 38 or 38a or provide the application to lines 39 and 39a of positive voltages 60 from several different origins.

A second stable state of the trigger corresponds to a conduction through transistor 36a. In that case output 37a takes a negative voltage while output 37 has a positive voltage. The state of the trigger may be switched either by a positive pulse directed into line 38a, or a positive voltage directed into line 39a. Obviously, this switching is accompanied by the reversal of respective potentials in lines 37 and 37a.

The trigger in Fig. 11a will be represented in Figs. 2a through 2k in the symbolic form of Fig. 11; reference letters however being possibly B, D, M, P, R, U or W. Identification of the lines will be apparent according to their origin and their connection to the right part or the left part of the square or to the upper or lower

to the middle of the lower part. Such a control is equivalent to a positive pulse simultaneously applied to inputs 38 and 38a. It has been noted already that only the pulses applied to the conductive side are effective. The time constants of the circuits are so calculated that only one switching then occurs. A spot inside the square on the right or the left side indicates the side which is conductive normally. It has been seen, in that case, that the corresponding output has a negative voltage.

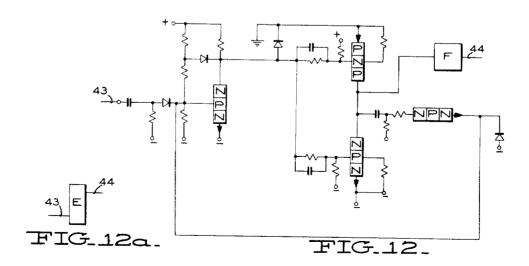

Fig. 12 shows schematically, a pulse emitter. A positive voltage directed into line 43 causes at output 44 the emission of a relatively short duration positive pulse. A circuit similar to that shown in Fig. 9 may be inserted in this output. The circuit of Fig. 12 is shown symbolically at Fig. 12a with reference letter E and is used essentially for delivering base pulses which will control the assembly of the circuits as explained hereafter.

Pulse generator.—The pulse generator is made up of four emitters 100a, 101a, 102a, 103a (Fig. 2j) working as a closed circuit. Further details of these emitters are shown in Fig. 12. They are controlled by positive pulses applied to their input terminal 43 and delivering in this case a very short duration positive pulse at their terminal 44. These pulses are fed respectively over lines 100, 101, 102, 103 (Fig. 2j) and are lagging in time as indicated in Fig. 3.

This pulse generator may be switched on or off in the conditions to be analyzed now. Capacitor 104 is normally charged positively through contact 105 and resistor 106. A manual or automatic action on contact 105 directs a positive voltage into line 107 and AND circuit 108. Lines 109, 110, 111 also have a positive voltage. Both the latter come from the non-conducting sides of triggers B2 and B3 (Fig. 2g) respectively. Subsequently, output 109 (Fig. 2j) of AND circuit 112 receives a positive voltage and likewise output 113 from AND circuit 108. This voltage is applied to OR circuit 114, to line 115, and to emitter 101a. The latter thus emits its first pulse, which causes the successive emission of pulses from elements 102a, 103a and 100a.

The first pulse transmitted through line 103 causes the switching of triggers B2 (Fig. 2j) and B3 (Fig. 2g) as will be seen later. AND circuit 112 (Fig. 2j) is thus blocked. Voltage in output line 109 subsequently is driven to a negative value, while voltage in line 117 from inverter 116 is driven to a positive value, which prepares the transmission of pulses through AND circuit 118.

When emitter 100a is set in action, the pulse on line 100 traverses AND circuit 118 and again controls 50 emitter 101a, this result being obtained through OR circuit 114. Subsequently, emitter 101a delivers a second pulse which in turn starts emitters 102a, 103a and 101a, then again 101a, etc.

To sum up, the chain formed by emitters 101a, 102a, 55 103a and 100a delivers a series of successive pulses, which series is indefinitely renewed as long as the voltages applied to AND circuit 112 remained unchanged.

Line 103 controls inverter 119 which feeds line 120 and AND circuits 121 and 121a. Trigger B1 being reset 60 as mentioned, output line 122a has a positive voltage, which thus favors AND circuit 121. The latter, which has been described in detail in Fig. 7, thus transmits a first pulse which causes trigger B1 to be switched. should be noted that line 120 initially has a positive voltage. Line 120 is driven to a negative voltage when emitter 103a is started and it has been seen that AND circuit in Fig. 7 then transmits no pulses. When pulse on line 103 stops, that is when line 103 comes back to a negative pulse, line 120 comes to a positive pulse and it is only at that time, as that has been seen, that AND circuit in Fig. 7 may transmit a pulse. The first switching of trigger B1 therefore coincides with the end of the first pulse on 103, that is with vertical line 126 in Fig. 3.

6

The state of trigger B1 (Fig. 2j) having been switched, line 122a comes back to a negative voltage, blocking AND circuit 121. Line 122, besides, comes to a positive voltage, favoring AND circuit 121a. A switching pulse thus may be applied to the left side of trigger B1 at the end of the next pulse on line 103. The time of this switching corresponds in Fig. 3 to vertical line 127.

Line 122a thus comes back to a positive voltage favoring again coincidence circuit 121 and preparing a new switching of the state of trigger B1, etc.

Generally speaking, the state of trigger B1 is switched every time line 103 comes back to a negative voltage. Lines 122 and 122a are traversed by alternate voltages alternately positive and negative as appears from Fig. 3.

Advance pulses.—A tapping from line 103 leads to AND circuits 123 and 123a, which again are fed respectively by lines 122 and 122a. Output lines 132 and 132a therefore, always have a negative voltage, except when positive pulses are applied simultaneously to two inputs of AND circuits 123 and 123a. These lines lead to inverters 124 and 124a, which respectively feed lines 125 and 125a. These lines then always have a positive voltage, except when positive voltages are directed simultaneously into AND circuits 123 and 123a. The purpose of lines 125 or 125a is to cause the switching of the various triggers as is to be seen later. Circuits controlled from these lines are so arranged as a general rule, that switching occurs when lines 125 or 125a come back to a positive voltage, and this switching subsequently coincides with the end of a pulse on line 103.

Registers and scanning chains.—In the embodiment of the invention which is being described, it was assumed that the registers comprised magnetic cores. It is known that, under certain conditions, certain magnetic substances possess two remnant states of saturation and that by distinguishing these states from one another it is possible to determine the presence or absence of an information bit. It is well understood that the use of memories of that type is not exclusive with respect to the invention. The selected record code is a mixed code associating binary elements 1, 2, 4, 8 with elements A, B and C. Such a code require seven magnetic cores for each position. It may be successfully used for numerical recording, alphabetic recording as well as the recording of certain special characters. Element C could be as desired, a parity or a no-parity controlling code. It will systematically be used in certain cases so that the number of elements serving to record a digit or a letter should always be even. Thus digit one will be recorded for example 1-C; digit 6 will be recorded 2-4 without element C, whereas digit 7 will be recorded 1-2-4-C. It will then be understood that the selected record code is not exclusive and is but illustrative.

The cores for a same position and the circuits connected therewith will conventionally be indexed with digits or letters 1-2-4-8-A-B-C, according to the element of the corresponding code. It is obvious that here, letters A and B have a completely different meaning from the meaning they had in the expressions Time A, Time B, scanning chain A, scanning chain B. There will result no confusion since none of these letters will ever be used alone.

With regards to the sign for some factors, it will be recorded as an element A if it is a "minus" sign. The absence of such an element will automatically mean a "plus" sign. Practically the sign will be recorded in each memory field in the less significant place. In some cases the sign may be stored in any position, when, for instance, a factor is directly recorded from a punched card or when the perforation representing the sign of this factor has been performed in any column of said card.

In each memory, there may be any number of loca-75 tions, said numbering ranging from a few units to sev-

eral times 10. However, it is to be noted that the invention has been specially planned to be conveniently used with great capacity memories.

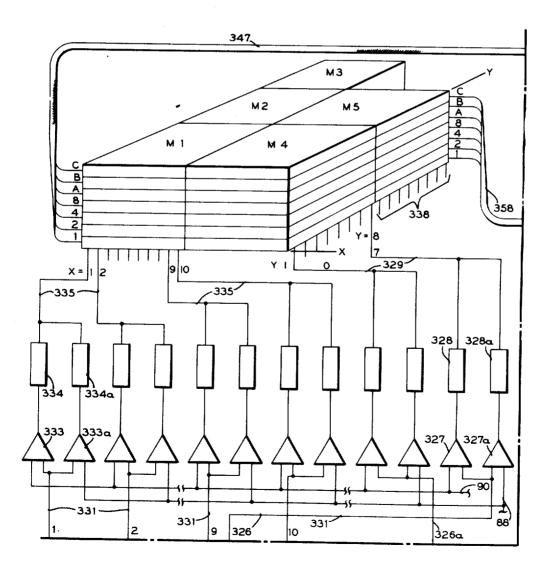

In the same way there may be any number of memories. As may be well understood and to avoid reproducing indefinitely identical circuits, five memories only have been represented in the enclosed drawings (Fig. 2h). Each register has been symbolically represented by seven superposed squares seen in perspective, each square corresponding to one element of the used code.

As an illustrative example, let it be assumed that each memory comprises 80 locations for recording 80 digits, letters or special characters. It will be remarked that each memory is able to register the whole of the information recorded in a punch card with 80 columns.

In each memory, the locations are grouped according to a coordinate system such as is represented in Fig. 12. Locations 1 to 10 of memory M1 for instance are defined by coordinates  $y=1, x=1, 2, \ldots 8, 9, 10$ . In the same way, locations 11 to 20 are defined by coordinates  $y=2, x=1, 2, 3 \ldots 8, 9, 10$ . It is well understood that this defining method is but illustrative and that any coordinate system could be used

$x=1 ext{ to 9}$   $y=1 ext{ to 9}$   $x=1 ext{ to 12}$   $y=1 ext{ to 7}$   $x=1 ext{ to 16}$   $y=1 ext{ to 5}$  $x=1 ext{ to 80}$

with possibly a few blank locations if the coordinate system defines a total memory location number which is superior to the actual location number.

The various locations of one memory are conventionally numbered in an increasing order according to a continuous numbering system going from one to 80. This numbering system is based on the custom of numbering the columns of a card according to a continuous system of numbers increasing from left to right. It is to be noted that this numbering method is exactly inverse to the method generally adopted for indicating the various adjacent digits of a number. Thus number 248 for example, will be recorded:

2 in location 14 4 in location 15 8 in location 16.

When it is desired to sense and read out that number (for instance to add it to another number) it is to be done character by character, beginning by the less significant weight digits. Consequently, there will be effected in turn the sensing and read out of the digit stored in location 16, then of the digit stored in location 15, etc. In other words, the various locations of a same memory will be scanned in the inverse order to their numbering.

So as to allow the free access to any location in any memory, scanning chains are associated with these memories the number of scanning chains corresponding to the number of addresses of the adopted operation type. A one-address operation would consist in effecting the elementary adding operation a+b=c, with the help of three different program stages, the first one controlling the transfer of factor a to an adding organ, the second one controlling the transfer of factor b, whereas the third one controls the registering of the adding operation result, this being indispensable to clear the adding organ and to permit its use in a second series of operations. Such an operating method requires but one scanning chain since each program stage controls but one operation.

A three-address operation would permit to effect the elementary adding operation a+b=c in one program stage. It requires three scanning chains. For the readout of factors a and b and the registering of the addition result are to be performed simultaneously.

8

In many cases, it is not advantageous to process in that manner and in particular when one factor is an accumulating element and when this factor becomes completely useless as soon as its function is performed. In such a case the factor may be replaced by the result of the operation. There results the double address operating type and to basic type of operation: a+b=b'. Factor b is an intermediate computing result which is determined but to value b' and is deleted as soon as its function is performed that is precisely as soon as b' is known. In such a case, two scanning chains will suffice, and it will again be noted that these chains have different functions: one chain controls the read-out and regeneration of factor a, and the second the read-out and deletion of factor b and its replacement by the result of operation b'

This double address operating type has been adopted in the embodiment being described. The scanning chains will be designated generally: chain A or chain B according to whether they control the read-out and regeneration of factor a or the read-out of factor b and its replacement by the result of operation b'.

The scanning chains are disposed in a fashion similar to that whereby the various locations of a memory have been distributed into groups of rows and columns (refer to Fig. 13). For example, chain A is subdivided into a unit chain for scanning the register according to abscissa x and a tens chain for scanning according to ordinate y.

The unit chain is composed of triggers 1U to 10U (Figs. 2c and 2d) wherein only the first two and the last two have been represented. The locations 1 to 10 and the positions that may be gathered therefrom by adding integer multiples of 10 are associated with these triggers. The various memory locations being scanned in the order inverse to their numbering, it will be likewise with regards to the normal advance of the unit chain, as will be seen hereafter.

The tens chain is composed of triggers 0D through 7D (Fig. 2b) wherein only the quoted triggers have been represented. With said triggers are associated respectively the first ten memory locations, then the next ten, and so on. As will be seen the normal tens chain advance is also effected in the order inverse to their numbering, so as to permit first the scanning of the memory locations bearing the numbers 80 to 71, then locations bearing the numbers 70 to 61. Generally the number of the triggers controlling the scanning of a given memory location is immediately determined by parting the digits of this number from each other. Thus location 27 is controlled by 50 triggers 2D and 7U respectively. There is one single exception for the locations having a number which is a multiple of 10, for example, location 30 is controlled respectively by triggers 2D and 10U, not by triggers 3D and 0U

Also triggers 1M, 2M, 3M . . . (Fig. 2a) for determining the memory according to its number are associated with scanning chain A. For example, if trigger 1M is switched, line 217 is at a positive voltage; and it will be the same for line 195 when AND circuit 194 allows the equalization of the voltages. Line 195 goes through OR circuits 323 and 323a which feed lines 324, 324a respectively. The latter will be positive whenever AND circuit 194 permits a voltage equalization, i.e., whenever line 188 is positive.

Line 324 controls AND circuits 325 (Fig. 2b) and 325a and lines 326 and 326a. Thus these lines may turn positive if one line 193 or 193a is positive that is if one trigger 0D to 7D is switched (the circuits corresponding to triggers 1D to 6D have not been represented). If trigger 7D is switched, for example, line 216 is positive causing line 190 to be at a positive voltage when line 188 is positive. It has been seen that the voltage of lines 195 (Fig. 2a) and of lines 324 and 324a were dependent on the voltage of the same line 188. Lines 326 and 326a (Fig. 2b) may also be seen in Fig.

2h. For example, line 326 controls AND circuits 327 and 327a, units 328, 328a and the line out of group 329 which is also indexed 7 or y=8; line 326a similarly controlling the line out of same group which is designated also by 0 or y=1.

Lead 324a (Fig. 2b) controls AND circuits 330 (Fig. 2c) 330a, 330b (Fig. 2d), 330c and lines generally designated by 331. Thus these last named lines may also turn positive if any line 191, 211, 332 (Fig. 2c) is switched. For example line 213 (Fig. 2d) is positive if trigger 1U is switched and it will be the same for line 191 when line 188 is positive, and line out of group 331 which is further designated by 1 (see also Fig. 2h) which well as the line out of group 335 which is referenced x=1.

As a conclusion the simultaneous switching of triggers 1M (Fig. 2a), 7D (Fig. 2b) and 1U (Fig. 2d) for example causes the respective energization of the lines out 20 of groups 335 (Fig. 2h) and 329 further designated x=1 and y=8 and consequently the memory location where these lines cross, that is location 71 of memory M1.

of trigger 2M (Fig. 2a) results in turning line 195a positive under certain conditions (line 188 being positive). Line 195a is connected through OR circuit 323a to line 324a which is the same line as previously mentioned controlling line group 335 (Fig. 2h). On the other hand a 30 second connection from line 195a reaches OR circuit 323b which controls line 336 (see also Fig. 2h) line group 337, as well as line group 338 (Fig. 2h). The circuits connecting both these groups have not been represented, but are similar to those connecting line groups 35 326 (Fig. 2b) and 329 (Fig. 2h). Line groups 335 and 338 cross one another in the memory field corresponding to the 80 locations of memory M2.

It will also be seen that the switching of trigger 3M (Fig. 2a) generally controls memory M3 (Fig. 2h), 40 connecting circuits being but partially represented. Likewise a trigger 4M (not shown) controls memory M4,

Scanning chain B is disposed in exactly the same way as chain A. It comprises a unit chain composed of triggers 11U to 20U (Figs. 2d and 2c), a tens chain composed of triggers 10D to 17D (Fig. 2b) and triggers 11M, 12M, 13M associated with it (Fig. 2a).

It will be noted that all these reference numbers are the same as for chain A, to which there is systematically 50 added 10; for example, a trigger 12M applies a voltage to line 195a and that is the line to which a voltage is applied when trigger 2M is switched, the only difference being that this voltage application takes place when line 265 is at a positive voltage. Under the same conditions, trigger 17D (Fig. 2b) for example causes a voltage application to line 193 which is also controlled by trigger 7D, whereas trigger 11U (Fig. 2D) applies a voltage to line 191. Generally speaking, chain B controls memories M1, M2, M3 . . . (Fig. 2h) just as does chain A with the only difference that this control now coincides with a positive voltage in line 265.

General operation principles .- Typical operations performed by the present machine include transfer operations and arithmetical operations performed on values 65 contained in memories. Assume for example the addition of two factors, say a and b, contained respectively in fields A and B of the memories and, in further assume b' as their sum, b' having to be substituted for b at the end or during the process of the operation.

For simplicity, suppose a and b are respectively 321 and 8765.

At a first operation time, read out of the first digit of a is performed, that is 1.

of b is performed, that is 5; then, the addition of 1 and 5 takes place producing the sum 6, then 6 is substituted Memory field B at that time contains for 5 in field B. the number 8766 instead of 8765 as before.

At a third operation time, read-out of the second digit, 2, of a is performed; then, at a fourth time of operation. read-out of the second digit, 6, of b is performed, then the addition of 2 and 6 takes place to produce the sum 8, and also substitution of 8 for 6. At that time memor 332a is positive itself that is if one trigger 1U to 10U 10 ory field B contains number 8786 instead of 8766 and 8765 as before.

At a fifth time of operation, the read-out of the third digit, 3, of a is performed; then at a sixth operation read-out of the third digit, 7, of b takes place. The controls AND circuits 333, 333a, units 334, 334a as 15 addition of 3 and 7 producing the sum 10 then occurs and 0 is substituted for 7.

Memory field B at that time contains 8086. Carry 1 is kept apart so that it is possible to recycle, should the occasion arise.

At a seventh time of operation, read-out of the fourth digit of a is performed, that is 0. If field A is completed, a series of 0's is introduced or substituted until the completion of field B.

At an eighth time of operation, read-out of the fourth In a similar way, it will be shown that the switching 25 digit, 8, of b, addition of this digit with the corresponding. digit read from field A or substituted, that is 0+8=8, possible recycling of the carry, that is in the case considered 8+1=9, and substitution of 9 for 8 takes place.

At that time memory field B contains 9086 which is the result of adding 321 to 8765.

It can be seen from the foregoing that the result of the addition is drawn progressively, digit by digit, and the working method used is characterized essentially by alternation of the read-out of digits from the two fields, the addition of these digits alternately read, and the substitution of the result of the whole operation for the digits read from field B.

These two times of operation are designated time A for a first and time B for the second.

The first time of operation is characterized essentially by a positive voltage of line 122a (Fig. 2j), and by various pulses controlled by this line. In a wider sense, the name "time A" is given to any time corresponding to a positive voltage of line 122a. The end of this time is marked by a return to a positive voltage of lines 120 and 125a, by the switching of trigger B1 due to a pulse from AND circuit 121a, and still by other switchings to be described further on, when necessary, which have no other purposes than to prepare for the next operations.

The second time of operation is characterized essentially by a positive voltage in line 122 as also various pulses controlled by this line. Likewise, in a wider sense, the name "time B" is given to any time corresponding to a positive voltage in line 122. The end of this time is marked by a return to a positive voltage of lines 120 and 125, by the switching of trigger B1 under action of a pulse from AND circuit 121, and still by another switchings to be examined further on when necessary and the purpose of which is also the preparation of the next operations.

It should be noted that the latter pulses mark the end of the operations relating to digits of a particular order.

Disposition and advance of the scanning chains.—The positioning of the scanning chains A and B will presently be described further. It has been explained how the various memory locations correspond to the various combinations of the tens and unit chains. For example, for location 72, triggers 7D (Fig. 2b) and 2U (Fig. 2d) in chain A are switched, whereas in chain B triggers 17D 70 and 12U are switched. Generally, it is possible to draw up a chart indicating the trigger combinations corresponding to every 80 memory locations. Under these conditions, the positioning of the scanning chains in location nof the memories is effected by the combined switching of At a second operation time, read-out of the first digit 75 corresponding triggers. The circuits for connecting the

80 hubs 153 (Fig. 2a) and the AND circuits generally designated by 203 and 204 (Figs. 2d to 2b) fulfill that condition.

With chain A for example in location 72 (switched triggers 7D and 2U), the chain is advanced as will be seen hereafter at the end of each time A whenever the voltage of line 181 (Fig. 2e) is turned positive. This movement coincides with a return of line 103 to a negative voltage (Fig. 2j). With lines 206 and 207 (Fig. 2e) respectively at a positive and a negative voltage, line 208 has the same voltage as line 181. A first switching pulse is produced when trigger B6 is switched (Fig. 2f); let it be assumed, as an example, that said pulse caused the switching of triggers 7D and 2U (see above). Lines 216 (Fig. 2b) and 339 (Fig. 2d) thus have a positive voltage. With line 188 positive (it is to be seen how that is done further on), AND circuit 190a passes the positive voltage to line 211 to condition AND circuit 212. AND circuit 212 receives its other input from line 208 to provide a switching pulse on line 340 which is applied to the left 20 side of trigger 2U resetting said trigger to its initial state, and to the right side of trigger 1U, causing this last trigger to be switched. Switched triggers are then 7D and 1U corresponding to memory location 71.

During the next succeeding time A, lines 213 and 191 are at a positive voltage. Consequently, at the end of that time, an advance pulse is transmitted by AND circuit 212a and line 340a and applied to the left side of trigger 1U and to the right side of trigger 10U (Fig. 2c). Trigger 1U is thus reset to its initial state, while trigger 10U is switched. At the same time the positive voltage of line 213 (Fig. 2d) is applied to OR circuit 209 (Fig. 2b) to line 210 and to AND circuit 215a.

Lead 188 is always at a positive voltage during time A and since trigger 7D is switched, lines 216 and 193 are at a positive voltage, which is applied to a second input of AND circuit 215a. There is no effect therefrom except when trigger 1U (Fig. 2d) is switched the voltage of line 213 is also applied to AND circuit 215a (Fig. 2b) as has just been explained. In that case, the latter transmits also an advance pulse, which results in re-setting trigger 7D to its initial state and switching trigger 6D (not shown). Under these conditions at the end of the considered time the switched triggers are triggers 6D and 10U respectively corresponding to the memory location

At the end of the following times A, triggers 9U, 8U, 7U . . . 2U, are switched in turn, whereas triggers 10U, 9U. . . are reset in turn. The result is the successive 50 control of trigger combinations 6D-9U, 6D-8U . . . 6D-2U, 6D-1U, corresponding to the memory locations referenced 69, 68 . . . 62, 61, respectively. Then there are controlled the trigger combinations 5D-10U, 5D-9U . . . corresponding to memory locations 60, 69, . . . . Generally speaking, all trigger combinations corresponding to the systematic scanning of the various positions of a memory are energized, scanning being effected in an order inverse to the numbering.

The scanning chains are connected in a ring, consequently it is necessary to stop the scanning operations when location 1 is reached to avoid going on through location 80. The trigger combination for this location is 0D-1U. Said triggers being supposed switched, line 213 and 216a (Figs. 2d and 2b) are at a positive voltage as are lines 191 and 193a during the following time A. A connection from these lines reaches AND circuit 341 (Fig. 2d) which is thus simultaneously energized on both its inputs, applying a positive voltage to line 342 thereby. 70 It was assumed that lead 206 (Fig. 2e) was at a positive voltage, thus AND circuit 343 has a positive voltage applied on both its inputs. A positive voltage is thus applied to OR circuit 291, which results in bringing the voltage of line 243 to a positive value. The result to 75 of an operation involving a sign search and a result in

12

be later described further is that scanning chain advance

The advance pulse may also be applied so that chain A scans the various memory locations according to their numbering increasing order. In such a case, it will suffice to turn line 206 negative (Fig. 2e) and line 207 positive. The voltage of line 181 is then applied to AND circuit 344 and to line 345 (see also Figs. 2c and 2b) which controls circuits so disposed that the scanning of the memory location is effected according to their number-The above explanations enable an undering order. standing of the operation of these last mentioned circuits, therefore they will not be described further. The scanning is stopped as soon as the chain reaches location 80, by the operation of AND circuit 346 (Fig. 2c) in a way similar to that just described.

The operation of chain B is quite similar to that of chain A, except that it is operated during time B under the voltage control of line 265 (Figs. 2b through 2f).

General control circuits.-It is necessary to cause each stage of program to start (and jointly to cause the setting out of action of the program just completed); to cause the setting of the scanning chains; to search for the nature of the arithmetical operation to be performed, the sign of each factor and the nature of the operation controlled being taken into account; to proceed, on occasion, to the search for the sign of each factor if it is not in its normal location; to proceed also to various operations of correction if the result of the arithmetical operation has not the anticipated sign.

The whole of these operations is controlled by triggers B3 through B13 (Figs. 2f and 2g) the functions of which, more particularly, are:

-setting into action each stage of the program and taking out of action the stage operated previously.

B4 setting into action the scanning chain which controls memory field A in order to search for the sign of the value contained in this memory field, if this sign is not in the lowest ordered position (for factor b, it is assumed that the sign always is located in the lowest ordered position).

B5-search for the sign of the value contained in memory field A if this sign is not in the lowest weight location.

-setting the scanning chains which control memory fields A and B in the locations of said fields corresponding to the lowest order.

B7-search for the sign of the values contained in memory fields A and B.

B8—(Fig. 2g) control of the arithmetical operation.

B9-various controls relating to digits of the lowest order. B10—check of digit exhaustion in memory field A.

B11-control of correction operations in the case of a complement result.

B12—(Fig. 2f) control of the addition and subtraction. B13—(Fig. 2g) control of the carries.

Triggers B3 through B11 are switched by pulses from line 125 (also refer to Fig. 2g), which pulses coincide in time with the switching pulse delivered by AND circuit 121, that is, with the end of a time B.

These triggers (B3 through B11) control each other, e.g., they form a chain; however, there are cases where two or several triggers may happen to be switched simultaneously. A better understanding of the circuits and how the different operations fit together will presently be discussed.

Trigger B3 always is switched at the beginning of the program and reset to its initial state at the end of the program.

The succession order of switchings and the period during which triggers B4 through B11 remain switched are variable according to the size of fields A and B, the sign location, and the result of the operation, a true value or a complement. This order is as follows in the case

14

true value and in the case of an operation without sign search but with a primary result in complement value: It will be assumed that the size of fields A and B are respectively 4 and 6 digits. An indication is also made of the time during which some of these triggers remain switched, when this period is higher than the period of times A and B.

(1) Operation with sign search and result in true value. The succession order of the switchings of triggers B4 through B11, is as follows:

**B4 B5 B6 B7** RR RQ B8 alone during three consecutive periods. B8-B10 during three consecutive periods.

(2) Operation without sign search but with a primary result in complement value:

**R7** B8 B9 B8 alone during three consecutive periods. B8-B10 during three consecutive periods. B11-B6 B11-B7 B11-B8-B9 B11-B8 during six consecutive periods.

Conditions under which triggers B12 and B13 are switched will be examined hereafter as necessary.

Start of a program stage.—Assume a connection linking hub 129 (Fig. 2j) with program step control hub 130 (Fig. 2e) connected to trigger P1. Trigger B2 (Fig. 2j) being initially restored as indicated in the drawing by a dot located on the right side in the square representing 40 symbolically this trigger, output line 110, at the same conductive side, has a positive voltage and impresses this positive voltage on hubs 129 and 130 (Fig. 2e) due to the above-mentioned connection. AND circuit 131 is thus conditioned to pass signals from line 134.

With trigger B1 (Fig. 2j) also restored, line 122a is at a positive voltage as is line 132a from AND circuit 123a when line 103 is positive. Thus, from an examination of Fig. 3, it may be seen that trigger B1 is switched only at the end of the first pulse delivered by line 103 (vertical line 126). Line 125a from inverter 124a is positive initially, and goes negative when the first pulse on line 103 appears.

Line 125a controls AND circuit 133 (Fig. 2g).

is positive, thus conditioning AND circuit 133. Output line 134 therefore will follow the voltage conditions of line 125a. This line leads to AND circuit 131 (Fig. 2e), and it is to be noted that the voltage on this line is initially positive. Therefore, no effect is produced when 60 lines 125a and 134 go negative.

As the pulse on line 103 ends (Fig. 2j), line 132a goes negative, thus causing a return to a positive voltage on line 125a. Line 134 follows so that a pulse at that time is transmitted through AND circuit 131 (Fig. 2e) which causes trigger P1 to switch. Output line 135 thus turns positive and likewise hubs 137, 138 and under certain conditions, hubs 139 and 140. The first hubs are connected to line 135 through diodes 141.

At the same time the voltage on line 134 is fed to AND circuit 142 (Fig. 2j) which now is conditioned to conduct due to line 110 which has a positive voltage. In a similar manner, trigger B2 is switched. Line 110 thus

(Fig. 2e), which previously prevents any new start of program P1. AND circuit 112 (Fig. 2j) henceforth is blocked, so that line 109 assumes a negative voltage. Inverter 116 restores a positive voltage to line 117, which then conditions AND circuit 118 and enables the generator of pulses to work continuously.

Before examining the action of the pulses delivered by hubs 137 through 140 (Fig. 2e) let us describe how trigger B3 (Fig. 2g) is switched. AND circuit 143 re-10 ceives on one side the line 111 and on the other side a connection from line 125 which are both initially positive.

When the first pulse on line 103 (Fig. 2j) appears, line 125 remains positive since AND circuit 123 remains 15 blocked due to line 122 which is negative. This line 122 becomes positive when trigger B1 is switched, but AND circuit 123 remains blocked due to the fact that line 103 has already come back to a negative level. When the second pulse on line 103 appears, AND circuit 123 is conditioned on both its inputs, thus producing a positive voltage on line 132 and a negative voltage on line 125, due to the presence of inverter 124. No effect on trigger B3 is produced (Fig. 1g) because of the particular arrangement of circuit 143. As the pulse on line 103 25 (Fig. 1h) ends, line 125 again becomes positive, causing the transmission of a pulse through AND circuit 143 (Fig. 2g), which in turn causes trigger B3 to switch and voltage in line 111 to come back to a negative value.

It should be noted that the switching of trigger B3 30 is shifted with respect to the switching of trigger P1 (Fig. 2e). The latter is performed at the end of a time A while the first is performed at the end of next time B. Within that interval various operations may be performed, which are to be analyzed now.

Search of the sign.—Assume that, for the moment, the program initiated from trigger P1 (Fig. 2e) controls the readout of a factor contained in a certain memory filed A and comprising a sign which is not in the location of that field corresponding to the lowest order. Connections as follows then are needed:

- (1) Hub 137 to one of hubs 146, i.e. hub 146a.

- (2) Hub 147a to one of the operation hubs (addition or subtraction) as will be discussed hereafter.

- (3) Hub 148a to one of hubs 149, i.e. hub 149n.

- (4) Hub 150n to one of hubs 152 (Fig. 2a) i.e. hub designated 152-1, if the sign is to be searched in the first memory unit.

- (5) Hub 151n (Fig. 2e) to one of the hubs 153 (Fig. 2a) i.e. to the hub also designated 71, if the sign 50 is to be searched in position 71.

With regard to the second of the above mentioned connections, it should be noted that the operation could have been controlled from hub 137 (Fig. 2e). Hub 147a serves the purpose of a repeater in case the number Since trigger B3 is also initially restored, output 111 55 of controls performed from the same hub should be more than one in order to limit the current. It is thus possible to arrange the circuits feeding hubs 137 and 138 (and all similar hubs) so that these circuits allow a single control to be effected; in connection with this, the normal function of hub 137 is the control of the nature of the operation (addition, subtraction, transfer), whereas the normal function of hub 138 is the control of the next stage of program. It is not possible to use the hubs this way if a sign search must also be effected, since then, one of hubs 137 or 138 would be assigned to a double control. The output hub 147a is thus provided as a repeater. The diodes such as 141, inserted between line 135 and hubs 137 or 138 or diode 154 inserted between hubs 146a and 147a may be replaced by circuits similar 70 to those represented in Fig. 9a.

It has been mentioned, trigger P1 (Fig. 2e) is switched before trigger B3 (Fig. 2g) is switched. The switching of trigger P1 corresponds in Fig. 2 to the time of vertical line 126, while the switching of trigger B3 correcomes back to a negative voltage as do hubs 129 and 130 75 sponds in time to vertical line 127. Line 135 (Fig. 2e)

subsequently has a positive voltage, as do hubs 137 and 146a (due to the connections previously mentioned). Line 155 is also at a positive voltage by virtue of the connection through diode 156.

Line 155 applies this positive voltage to one of the inputs of AND circuit 157 (Fig. 2f). At the same time a positive voltage is applied to the second input through line 158. The latter comes from the non-conductive side of trigger B11 (Fig. 2g). Output line 159 (Fig. 2f) is thus positive to condition AND circuits 160 and 161 to conduct. Line 162 has a negative voltage due to the presence of inverter 163. AND circuits 164 and 165 are thus blocked.

It should be noted that AND circuits 161 and 165 are connected to line 145, which comes from the left side 15 of trigger B3 (Fig. 2g). Initially, this line has a negative voltage, but will turn positive once trigger B3 is switched. Transmission of a pulse is taken therefrom through one of AND circuits 161 or 165 (Fig. 2f) which causes triggers B4 or B6 to be switched. It should be noted 20 that this switching depends on the voltage conditions of lines 159 and 162, which in turn is dependent on the voltage condition of line 155 (Fig. 2e). Depending on whether or not a sign search is to be made, the trigger chain of Fig. 1f will be started at B4 or B6. It has been assumed that a connection linked hub 137 (Fig. 2e) with hub 146a, so that line 155 would have a positive voltage and switch trigger B4.

Switching period of trigger B4.—Switching of trigger B4 is performed at the end of a time B. This trigger remains switched during next times A and B and resumes its initial state at the end of this time. During this period, line 166 (Fig. 2f) assumes a negative voltage, blocking AND circuits 167 (Fig. 2g) and thus 168. Line 169 is thus negative. The latter leads to AND circuit 170 (Fig. 2e) blocks and makes negative hub 139. Connections achieved from this hub thus are made inoperative. Line 171 (Fig. 2f) assumes a positive voltage (due to the switching of trigger B4) and conditions AND circuits 172, 173, 174. This results in the following:

Since line 122a also has a positive voltage (time A) line 175 from AND circuit 172 and line 176 from OR circuit 177 assume a positive voltage level. Line 175 leads to AND circuit 178 (Fig. 2e) which is already conditioned on its second input due to the positive voltage of hub 146a. Voltage of hub 148a therefore assumes a positive level as does hub 149n to which 148a is connected. With line 176 also positive, AND circuit 179 produces an output to hubs 150n and 151n. Hub 152-1 (Fig. 2a) and hub 153 referenced 71 thus assume a positive voltage level due to the fourth and fifth above-mentioned connections. The result is the activation of AND circuit 200 and the application of a positive voltage to lines 201-1 and 202-7. Line 201-1 passes through Fig. 1b and 1c and leads to AND circuit 203 (Fig. 2d). Line 202-7 (Fig. 2a) leads to AND circuit 204 (Fig. 2b).

A connection from line 176 designated 176a (Fig. 2e) passes through Figs. 2e, 2d, 2c, 2b, 2a, and leads to AND circuit 203 (Fig. 2d) which enables control of trigger 1U, AND circuit 204 (Fig. 2b) which enables control of trigger 7D, and AND circuit 182 (Fig. 2a). At the end of time A, the voltage on line 103 (Fig. 2j) goes positive as does the voltage on line 132a since the voltage on line 122a is then positive. Line 132a leads to AND circuit 182 (Fig. 2a) which is conditioned by the positive voltage on line 176a. Line 144 thus applies a positive voltage to the right side of trigger 1M through AND circuit 200, causing this trigger to be switched.

As has been discussed, trigger 1M controls the first 70 memory unit.

AND circuit 173 (Fig. 2e) receives on its second input the voltage of line 125a. Output line 180 follows the voltage conditions of the latter as does line 181. The latter leads to AND circuit 205 (Fig. 2e). Suppose that 75 225 subsequently have a positive voltage, conditioning

16 line 206 has a positive voltage (line 207 having a negative voltage), then line 208 has a positive voltage level which traverses Figs. 1d and 1c and leads to AND circuit 215 (Fig. 1b). When line 176a has a positive voltage so does line 210, OR circuit 209 equalizes the voltages.

The foregoing lines and circuits will thus follow the voltage conditions of line 125a (Figs. 2e through 2h).

It has been seen that AND circuit 203 (Fig. 2d) has a positive voltage applied to both its inputs. The output line therefore is at a positive voltage as is line 211 which leads to AND circuit 212. The latter receiving its second input from line 208, will transmit a first switching pulse which is directed to the left side of trigger 2U and to the right side of trigger 1U. This does not trigger 2U, due to the fact that this trigger already conducts at its right side. On the other hand, trigger 1U is switched, and thus gives line 213 a positive voltage level.

The voltage on line  $21\overline{4}$  (Fig. 2b) is also positive and results in a second switching pulse transmitted through AND circuit 215, which causes trigger 7D to switch.

Triggers 1U and 7D control the location of memory designated 71, which is that containing the sign as was assumed. Switching of triggers 1U and 7D is performed at the end of a time A. Sensing of the corresponding location in the memory will be performed during next time A, under control of trigger B5 (Fig. 2f).

In summary, switching period A of trigger B4 corresponds to the operation of the organs controlling the location of the memory to which access is to be given. Nothing occurs during time B, except, at the end of this time, the return of trigger B4 to its initial state and the control of trigger B5. This result is obtained through AND circuit 174 which receives on its second input the voltage of line 125. This results in a switching pulse at 35 the end of time B; which pulse is directed to the left side of trigger B4 and to the right side of trigger B5. Trigger B4 thus comes back to its initial state, while trigger B5 is switched.

Switching period of trigger B5.—The voltage on line 183 becomes positive, and conditions AND circuits 184, 185, 160, 186 and starts the following sequence during time A:

AND circuit 184 has its second input connected to line 122a. The latter has a positive voltage thus lines 187, 188 and 189 will assume a positive level. A connection from line 188 traverses Figs. 2e through 2a. It leads first to AND circuit 190b (Fig. 1d) which is conditioned by its second input due to the switching of trigger 1U. Line 191 thus assumes a positive voltage.

A second connection from line 188 leads to AND circuit 192 (Fig. 2b) which is conditioned by its second input due to the switching of trigger 7D and due to the fact that line 216 has a positive voltage. Subsequently, the voltage on line 193 is also positive.

A third connection from line 188 leads to AND circuit 194 (Fig. 2a) which also is conditioned at its second input by the switching of trigger 1M. Subsequently, voltage on line 195 is positive. The general effects thereof will be examined later.

When line 196 (Fig. 2f) is positive, AND circuit 197 is conditioned at both its inputs, which develops a positive voltage on line 198. This line controls AND circuits 219, 220 (Fig. 2j) (effects thereof will be discussed later). For the present, let us simply observe that positive voltages on lines 191, 193, 195 and 198 control the read-out and re-write of the value contained in the memory position where access is to be had, and that the reading of this value is performed during these opera-Trigger AR (Fig. 2i) will be switched if this value bears "minus" sign which develops a positive voltage in line 99. This line goes to AND circuits 221 (Fig. 2g), 222 and 223 (Fig. 2f).

AND circuit 160 is connected to line 159, which has a positive voltage in the case considered. Lines 224 and

AND circuit 226. The latter receiving its second input from line 125a thus voltage on output line 227 follows the same variations.

It has been seen that the circuits controlled from line 125a essentially served the purpose of emitting various switching pulses. Consequently, in the case considered, a switching pulse is emitted by AND circuit 222, and applied simultaneously to both sides of trigger B12, which causes this trigger to switch its state. Voltage on line 96 thus goes positive.

Obviously, this switching of trigger B12 takes place only if line 99 has a positive voltage, that is if trigger AR (Fig. 2i) has been switched. As is to be seen, the switching of this trigger corresponds to the sensing of sign "minus" (so that this switching does not occur in 15 the case of the sensing of a sign "plus," in which case the voltage on line 99 is negative).

It should be noted that there is no advance here of the scanning chains at the end of time A. The advance is controlled by the voltage on line 181 (Fig. 2e) which 20 now is negative due to the fact that voltage on line 180 is negative, as is that on line 229. At the end of time A trigger B1 (Fig. 2j) is switched, and by the return of voltage in line 122a to a negative value, voltage in line 122 becomes positive.

During time B, voltage on line 132 goes positive, when voltage on line 103 goes positive. Line 132 is connected to AND circuit 185 (Fig. 2e), the other input of which is at a positive level. The voltage on line 230 thus becomes positive. This line may be traced back through 30 Figs. 2e through 2a to the left side of triggers 1U through 10U (Figs. 2c and 2d) 0D through 7D (Fig. 2b) and 1M through 3M (Fig. 2a); these triggers that were switched (1M, 7D and 1U) thus are all restored to their initial state.

It has been seen that AND circuit 186 (Fig. 2f) also was conditioned. Line 125 feeds the second input of this AND circuit to produce a switching pulse at the end of time B which causes trigger B6 to switch its state and trigger B5 to be restored to its initial state.

Switching period of trigger B6.—Line 231 has a positive voltage, which conditions AND circuits 233 and 234. This line leads also to OR circuits 232 and 177, so that lines 176, 176a and 235 are also positive.

It has been seen that trigger P1 (Fig. 2e) had been 45 switched and mention has been made also that hubs 137 and 138 respectively served the purpose of controlling the nature of the operation and the next program stage. Hub 139 serves the purpose of controlling the memory field operating to read-out, whereas hub 50 140 serves the same purpose for the memory read-out and substitution. Connections must be made as fol-

(1) Hub 139 to one of hubs 149, i.e. hub 149b.

(2) Hub 150b to one of hubs 152 (Fig. 2a), i.e. hub 55 152-1 if the memory field controlled for read-out corresponds to memory 1.

(3) Hub 151b (Fig. 2e) to one of hubs 153 (Fig. 2a) i.e., to that of hub also designated 71 if the digit of lowest order in the subtrahend is in location 71 (the same digit as above has been chosen for the sole purpose of avoiding the description of a plurality of similar circuits).

(4) Hub 140 (Fig. 2e) to one of hubs 149, i.e. hub **149***p* (not shown).

(5) Hub 150p (not shown) to one of hubs 152 (Fig. 2a) i.e. hub 152-2 if the memory field controlled for read-out and substitution corresponds to memory 2.

(6) Hub 151p (not shown) to one of hubs 153 (Fig. 2a), i.e. to that of hubs also designated 71 if the digit of lowest weight in the subtrahend is in location 71 (the same digit as above has been chosen for the purpose of simplifying the description and avoiding a complete new description of a plurality of similar circuits).

the purpose of defining the nature of the operation particularly to hub 236 (Fig. 2f) if this operation is to be a subtraction.

The circuit feeding hub 137 (Fig. 2e) as a rule, is so constructed as to allow only the operation of a single control. Accordingly, connections must be made in a slightly different way if a search for signs is to be performed. In this case, hub 137 must be connected to one of hubs 146, i.e. hub 146a, and the repeating hub 147a which must be used to control the operation, and this hub is consequently connected to hub 236 (Fig. 2f) if the operation is a subtraction. Hub 137 (Fig. 2e) is positive as are hubs 146a, 147a and accordingly hub 236 (Fig. 2f) and line 237.

Line 238 (Fig. 2g) is connected through OR circuit 10 to line 122. The voltage on line 238 is thus posi-240 to line 122. tive at each time B.

When trigger B11 is switched, line 241 is constantly positive, during during times A as well as times B, and consequently line 238 will be positive during this time.

Line 169 is connected to line 122a through AND circuit 168. Therefore it is positive for certain times A, more particularly every time line 242 is positive. The latter depends on AND circuit 167; it is positive every time voltages applied to this circuit are positive simultaneously, that is, every time triggers B4 (Fig. 2f) and B11 (Fig. 2g) are in their initial state. Voltage in the same line is negative every time any one of triggers B4 or B11 is switched. From the foregoing, the conditions under which hubs 139 (Fig. 2e) and 140 emit pulses are established.

Following are the results of switching trigger B6 (Fig. 2f):

Time A.—Line 169 (Fig. 2g) is positive as thus are hubs 139 (Fig. 2e), 149b (due to one of the above-mentioned connections), 150b, 151b (due to the positive level of line 176 at AND circuits 179b), 152-1 (Fig. 2a) and 153 also designated 71.

The positive voltage of hub 152-1 conditions AND circuit 200 which receives a second positive pulse from line 144. The result is the switching of trigger 1M, as already mentioned. At the same time, the positive voltage of hub 153 designated 71, causes the voltage on one of the lines of each group 201 and 202 to be positive to thus condition AND circuits 204 (Fig. 2b) and 203 (Fig. 2d.)

Line 243 (Fig. 2e) at this time has a negative voltage level. This line leads to inverter 244 (Fig. 2e.) Line 245 thus has a positive voltage, which conditions one of the inputs of AND circuit 246. This AND circuit receives on its second input the voltage of line 235, which also is positive. Then it allows a positive voltage to pass, which is applied to AND circuit 247. The latter receiving on its second input the voltage of line 125a, output line 229 follows the same voltage conditions as does line 181. The latter leads to AND circuit 205 (Fig. 2) which at present is conditioned to conduct by the positive voltage on line 206. Under these conditions, line 208 follows the same voltage conditions as exist on line 125a. Consequently, at the end of time A, triggers 1U (Fig. 2d) and 7D (Fig. 2b) are switched.

Scanning of memory location designated 71 is thus made possible as will more clearly appear hereafter.

Time B.—Line 238 (Fig. 2g) is positive and as a result hub 140 (Fig. 2e) is made positive. Hub 149p (not shown) is positive due to one of the above-mentioned connections. Hub 150p (not shown) and hub 151p (not shown) are at a positive potential due to an AND circuit 179p (not shown) and to the fact that line 176 is positive. Hub 152-2 (Fig. 2a) and hub 153 designated 71 are at a positive level because of the above-mentioned plug connections.

One of the lines of each group 201 and 202 thus takes (7) Hub 137 (Fig. 2e) to one of the hubs which serve 75 a positive voltage, that is, line 7 of group 202, and line

1 of group 201. These lines are the same as those which were positive at time A, however, the results produced thereby are different. At the present time B, AND circuits 204 (Fig. 2b) and 203 (Fig. 2d) under control of line 7 of group 202, line 1 of group 201 and line 176a supply positive voltages to lines 214 (Fig. 2b) and 211 (Fig. 2d) since line 176a is positive. However, switching pulses are no longer delivered by line 208, but are delivered by line 208a. The voltage on the line 125a (Figs. 2f and 2g) remains unchanged during 10 a time B, thus only circuits controlled from line 125 can deliver switching pulses. The latter feeds AND circuit 248 (Fig. 2e) which is conditioned on its second input by AND circuit 246. Line 249 thus responds to voltage conditions on line 125. Assuming that line 15 206 (Fig. 2e) has a positive voltage (and line 207 a negative voltage), line 208a responds to voltage conditions on line 249 through AND circuit 205a. Line 208a feeds AND circuit 212b (Fig. 2d) which is conditioned at its second input by line 211, now positive, to deliver 20 a pulse which causes trigger 11U to be switched. Line 208a also feeds AND circuit 215b (Fig. 2b) which also is conditioned on its second input due to the fact that lines 214 and 210a are positive. The result is a second pulse which causes trigger 17D to be switched. The 25 scanning chain constituted by triggers 11U through 20U (Figs. 2c and 2d) and 10D through 17D (Fig. 2b) is that way started to allow the scanning of a second memory position designated 71.

It has been seen that hub 152-2 (Fig. 2a) is at a positive voltage. AND circuit 250 thus is conditioned. At the end of time B, line 103 (Fig. 2j) becomes positive and through AND circuit 123 causes line 132 to go positive. Line 132 feeds AND circuit 251 (Fig. 2a). Line 176a is positive thus output line 252 is positive and subsequently the output from AND circuit 250. A positive voltage thus is applied to trigger 12M and causes it to switch.

It also has been seen that AND circuit 233 (Fig. 2f) was conditioned at one of its inputs due to positive line 40 231. This AND circuit may be activated if a connection has been made to hub 236. A line connected to line 125 and to AND circuit 233 causes leading to this element, a pulse to be emitted from AND circuit 233 to switch trigger B12.

Finally, another line connected from line 125 leads to AND circuit 234 which emits a pulse at the end of time B to cause trigger B7 to be switched and trigger B6 to be restored to its initial state.

Switching period of trigger B7.—Line 253 has a positive voltage which conditions AND circuits 254 (Fig. 2j), 256 (Fig. 2f), 257 and 164. Lines 258 (Fig. 2g) and 259 also have a positive voltage supplied through OR circuits 260 and 261 thus conditioning AND circuits 263 and 262 (Fig. 2f). This results in the following:

- (1) Time A.—Line 122a has a positive voltage. Consequently a positive voltage is impressed on lines 264 (Fig. 2f), 188 and 198 and as was described under the heading "Switching Time of Trigger B5," lines 191 (Fig. 2d), 193 (Fig. 2b), and 195 (Fig. 2a) are at a positive level. These different voltages control the sensing of memory 1 at designation 71 (assuming connections set up corresponding to that location). It will be explained later how this sensing is performed. For the present, only the results will be discussed, particularly the switching of trigger AR (Fig. 2i) and the positive voltage feed of line 99 in case a "minus" sign would happen to be entered in the position considered. Two cases will be considered:

- (a) The case of a sign search. Where the sign of the factor to be read from memory 1 is located at some position other than the lowest order and the sign if any in the lowest order is for another factor. This may be the case, for example, if the quantity which is to be recorded in memory 1 is from the sensing of a punched card. It

is known that perforations in such cards can correspond first to a digital or alphabetical code, and the sign of a given factor contained in that card often is embodied in the form of a perforation designated "11" which may be in any column. The sign of a quantity punched in columns 65 through 71 for example may be in column 27. If the whole of the card has been entered in a memory i.e. memory 1, and if entry has been so performed that to each column in the card corresponds a memory location bearing exactly the same number, it is necessary to scan position 27 in order to get the sign and then scan locations 65 through 71 in order to have the factor.

In the case of a sign search, it has been seen that it is necessary to provide a connection between hubs 137 (Fig. 2e) and one of hubs 146, and that lines 155 and 159 (Fig. 2f) then have a positive voltage. Voltage on line 162 is negative, which blocks AND circuits 164 and 226.

(b) The case of no sign search where no connection has been made between hubs 137 (Fig. 2e) and 146. The voltage on lines 155 and 159 (Fig. 2f) is negative whereas voltage on line 162 is positive. AND circuit 164 is conditioned at both its inputs, which produces a positive voltage on line 225 and thus conditions AND circuit 226. Line 227 then follows the voltage conditions of line 125a, which causes a switching pulse to be transmitted through AND circuit 222 if line 99 also has a positive voltage, that is, if trigger AR (Fig. 2i) has sensed the presence of a minus sign in the memory location being scanned.

It should be noted that at the end of time A, trigger AR (Fig. 1j) is reset, and generally speaking, of all triggers bearing suffix R are reset at this time. Voltage on line 120 (Fig. 2j) initially is positive, and becomes negative when the pulse on line 103 come up. This voltage is directed into AND circuit 199 (Fig. 2g) which has its second input connected to ground. Subsequently output line 98 follows the voltage conditions of line 120. This line leads to Fig. 2i and controls the reset of triggers with suffix R.

Line 98 goes positive at the beginning of time A, so that a first reset cannot occur at that time. Switching of trigger R occurs at time A, coinciding with a pulse from line 101 (also refer to Fig. 2j). Voltage on line 98 then is invariable. It turns negative when pulse 103 comes up to take back a positive value at the end of this pulse, which coincides with the end of time A. Thus, a positive voltage is directed into all the triggers R (Fig. 2i) which causes all these triggers to come back to their initial state.

On the other hand, it should be noted that no pulse is developed which causes scanning chains to advance, that is, which controls the triggers with suffixes U (Figs. 55 2d or 2c) or D (Fig. 2b).

(2) Time B.—When the voltage on line 122 becomes positive, AND circuit 263 (Fig. 2g) allows a positive voltage to pass to line 265. Line 265a leads to OR circuit 266, so that lines 189 and 198 also have a posi-60 tive voltage.

Line 265 traverses Figs. 2e through 2a, and conditions AND circuits 190a, 192a and 194a. Trigger 11U (Fig. 2d) having been switched, AND circuit 190a is conditioned with both its inputs, which imparts a positive voltage to line 191. Likewise, triggers 17D (Fig. 2b) and 12M (Fig. 2a) have been switched, which conditions AND circuits 192a and 194a, and imparts a positive voltage to lines 193 (Fig. 2b) and 195a (Fig. 2a). These voltages control the sensing of the memory location to which connections are assumed, that is location 71 in memory 2. This sensing will be described later. It should be noted now that a switching of trigger AR (Fig. 2i) may occur if the corresponding memory location contains a minus sign, which imparts a positive

voltage to line 99 and conditions AND circuit 223

AND circuit 256 receiving an input from line 125 and line 167 follows the voltage conditions of line 125 so that AND circuit 223 may allow a switching pulse to pass, under conditions similar to those mentioned in the foregoing. This pulse is applied to trigger B12.

It should be noted that AND circuit 254 (Fig. 2j) is used for the purpose of re-writing the quantity sensed Line 97 then made positive feeds AND circuits 355 10 (Fig. 2i). These circuits normally control the re-write at time A. Re-write at time B is normally controlled by AND circuits 363. The latter can be used in the case considered since adder 360 is not yet operating.

AND circuit 257 (Fig. 2f) receives on its second 15 input a line from line 125. It delivers, at the end of time B, a switching pulse which causes the reset of trigger B7 to its initial state and triggers B8 and B9 (Fig. 2g) to be switched.

It should be noted that no pulse is applied to the 20 chain constituted by triggers 11U through 20U and 10D. through 17D (Figs. 2b through 2d).

Switching period of triggers B8 and B9.-Trigger B8 controls arithmetical operations. It remains switched until the factors are exhausted. Trigger B9 more par- 25 ticularly controls the operations relating to the unit digits. In order to give a clear understanding, the example in the foregoing is taken again, that is the addition of factor a=321 with factor b=8765, the result of the addition being substituted for b. So far, it has been supposed that the unit digits of factors a and b were respectively in location 71 of memories 1 and 2, but let us suppose now that these factors respectively are in locations 72 through 75 of memory 1 for factor a, and locations 72 through 77 in memory 2 for factor b, scan- 35 tion processes as follows: ning chains being, at the beginning of these operations respectively in locations 75 and 77. Factor a is controlled by chain A whereas factor b is controlled by chain B.