Filed Dec. 23, 1957

32 Sheets-Sheet 1

FIG. 1.

INVENTORS EUGENI ESTREMS MAURICE PAPO

ATTORNEY

Filed Dec. 23, 1957

FIG\_ 2a\_

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

| 4 ф.          | 4.04.                             | 편IG.<br>**   |         |            |  |

|---------------|-----------------------------------|--------------|---------|------------|--|

| F19.          | FIG.                              | ₽1₽<br>*     |         |            |  |

| FIG. FIG.     | F1G<br>4 4                        | FIG.         |         | FIG.<br>2b |  |

| FIG-          | FIG. FIG. FIG. FIG. FIG. 4h 4h 4m | 구.<br>구.     |         | FIG.<br>2a |  |

| F 4<br>Q 0    | 4r<br>4r                          | 4t.          |         |            |  |

| FIG.          | 파10-<br>년                         | FIG.         |         |            |  |

| 년<br>4<br>0 대 | 4.i.4                             | F1G.         | FIG- 5- |            |  |

|               | 파IG.<br>44h                       | 년<br>44<br>유 | 4       |            |  |

|               |                                   | 和G.          |         |            |  |

# Oct. 15, 1963 E. ESTREMS ETAL

3,107,342

EDITING MACHINE

Filed Dec. 23, 1957

TIG\_ 4a\_

Filed Dec. 23, 1957

TIG. 4b.

FIG. 4c.

FIG\_4d\_

FIG\_ 4e\_

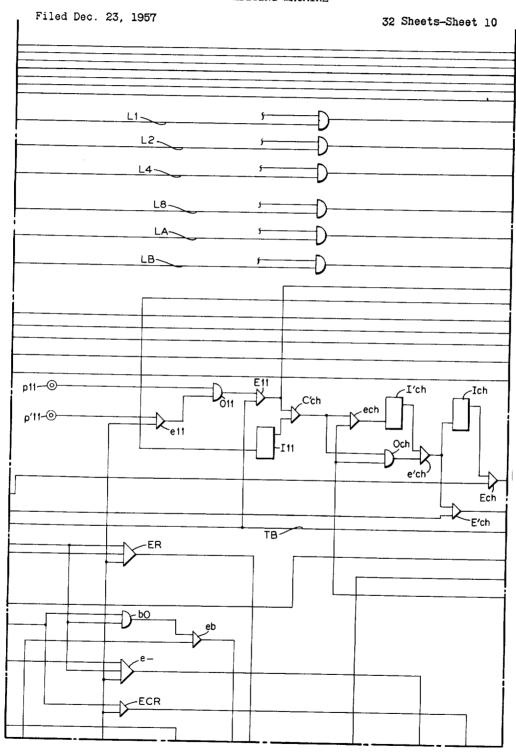

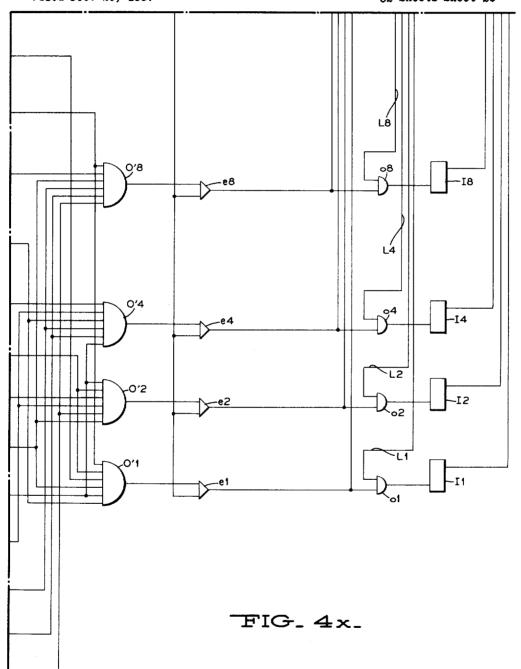

EDITING MACHINE Filed Dec. 23, 1957 32 Sheets-Sheet 11 L1-L4-L8-LB-

TIG\_ 4f\_

Filed Dec. 23, 1957

TIG\_ 4g.

Filed Dec. 23, 1957

FIG. 4h.

Filed Dec. 23, 1957

FIG\_ 4i\_

Filed Dec. 23, 1957

FIG- 4j-

Filed Dec. 23, 1957

FIG\_4k\_

Filed Dec. 23, 1957

TIG\_ 41\_

Filed Dec. 23, 1957

FIG\_4m\_

Filed Dec. 23, 1957

FIG\_4n\_

Filed Dec. 23, 1957

TIG\_ 40-

Filed Dec. 23, 1957

Filed Dec. 23, 1957

Filed Dec. 23, 1957

# Oct. 15, 1963 E. ESTREMS ETAL

3,107,342

EDITING MACHINE

32 Sheets-Sheet 24 Filed Dec. 23, 1957 ŢΑ TIG\_4s\_

Filed Dec. 23, 1957

TIG\_4t\_

Filed Dec. 23, 1957

FIG. 4u\_

Filed Dec. 23, 1957

FIG. 4v.

Filed Dec. 23, 1957

FIG. 4w.

Filed Dec. 23, 1957

Filed Dec. 23, 1957

FIG\_6a\_

Filed Dec. 23, 1957

TIG\_ 10\_

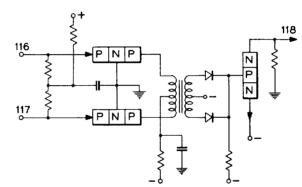

116 A 118

FIG-11b-

FIG\_lla\_

FIG. 12a.

Filed Dec. 23, 1957

TIG\_ 13\_

1

# 3,107,342 EDITING MACHINE

Eugeni Estrems, Saint Mande, and Maurice Papo, Paris, France, assignors to International Business Machines Corporation, New York, N.Y., a corporation of New York

Filed Dec. 23, 1957, Ser. No. 704,782 27 Claims. (Cl. 340-172.5)

This invention relates to a machine used for editing information and which may be utilized in accounting machines, calculators, etc.

To make it more convenient, even though the data are not necessarily assembled according to lines and may laneous number of information and composed during a machine operating cycle will be indicated as an "information line."

In previous electrical accounting machines, the editing of an information line is usually performed through intricate mechanical devices, slow and cumbersome. For the transfer of the information to the printing mechanisms, these devices require a connection for each character or position of the line to be composed; for example, in order to compose an 80 position line, 80 connections must be wired. Not only does this large number of connections hinder the machine control panel, but still, in case it is desired to compose differently 2 lines, it is necessary to use a certain number of selectors having in total as many transferable contacts as there are connections to be switched according to the above example, if, in the 2 lines to be composed, the distribution of the information is different for the 80 positions, 20 selectors with 4 transferable contacts for example, are necessary; according to the occupied state, normal or transferred, these selectors allow the composition of the line according to one or the other of the selected types.

A primary object of this invention is to provide an improved data processing machine.

Another object of this invention is to provide improved editing apparatus for a data processing machine.

Another object is to provide editing apparatus of improved flexibility.

A further object is to provide more easily operated controls for editing apparatus.

Another object is to provide editing apparatus with wider utility.

Another object is to provide improved editing apparatus allowing a complete redistribution of data in a single

Another object is to provide improved editing apparatus wherein a plurality of characters may be selected by a single control wire.

Another object is to provide improved apparatus for inserting special symbols at locations determined by the data being processed.

Another object is to provide improved apparatus for effecting a floating \$ operation.

Still another object is to provide editing apparatus of improved speed.

Another object is to provide an editing machine of high versatility.

A still further object is to provide an editing machine of economic construction with high versatility.

Another object is to provide an editing machine with serial operation and improved speed.

Another object is to provide an improved editing machine requiring fewer plug connections.

Another object is to provide an editing machine requiring fewer selectors for changing a format.

A more particular object of this invention is to pro-

2

vide an improved zero suppression apparatus for an editing machine.

Another object is to provide an editing machine with improved sign detecting apparatus.

The present machine provides for the composition of an information line in a storage device, the format of which line may vary from one machine cycle to the other. Control circuits are associated with each position of said storage device in order to control the elimination, the replacement or the insertion of a whole or a part of an information element, while conserving space on the control panel, especially by reducing the number of selectors necessary to change the format of the line to be transferred later to any display device such as a printbe arranged in any manner, a group including a miscel- 15 ing or punching mechanism, for example. This editing machine allows the recording to the output storage of an information line with all its details, thus making up the complete picture of the line to be printed, punched,

The present machine may perform simultaneously a redistribution of the information, the erasing of certain characters, the substitution or the insertion of one or several miscellaneous characters which may, for example, make up fixed words. The arrangement of these circuits is such that it is sufficient to control an operation at a determined position, in order that this operation be automatically performed during the following position (or positions) until the control of another operation is reached. The insertion of characters may be unconditional or, for example, depend on the sign of the quantity to be printed. The position where the character is to be inserted may also, either be arbitrarily determined, or depend on certain conditions, such as: the character may be printed in the position to the left of the first significant digit of the quantity to be printed.

The information line may be composed during a direct scanning (from right to left) of all its positions, then it is retouched by an opposite scanning (from left to right) just before the display, the printing, etc., so that the output storage contains the very picture of the information line that will be displayed, printed, etc. During the direct scanning, transfers, insertions, suppressions or substitutions may be performed. During the opposite scanning, substitutions may still be performed, so that, after the opposite scanning, the information line be completely composed.

The composition of an information line is an operation which may be performed in a single program step, and once the line has been composed, the display, the printing, etc., is controlled by a single program step, regardless of the number of characters included in the line. After controlling the display, printing, etc., the output storage is reset, that is a blank is recorded in all the positions of the storage, in order that it be ready to receive the information to be reproduced in the following line.

The operating times for an editing program are synchronized with the computing cycles so that the same selectors may be used indifferently for computing or editing.

The machine is provided with several devices that enable numerous types of editing to be done.

A special device, controlled by a single connection allows the insertion, at the beginning of the quantity to be printed, of one or several check protection asterisks, the number of asterisks to be inserted are automatically determined according to the first significant digit of the quantity to be printed. In prior devices, in order to insert these asterisks, a relay was necessary for each position that might be occupied by an asterisk.

Another device allows to record a dollar sign in the next position to the left of the high order significant digit

and consequently must first determine the position into which the dollar sign is to be printed.

Another device allows the erasure of certain characters, that is, either a single blank may be inserted or a continuous series of blanks. During this insertion, as 5 during all the others, the information transfer is interrupted. In order to insert a series of blanks, it is sufficient to wire 2 connections that determine the two positions between which the blanks must be inserted.

The print edit is performed according to a general rule; 10 only exceptions need be wired. Thus, another device erases automatically the zeros on the right of a blank, and this suppression is stopped upon reading the first significant digit. This function is performed during the opposite scanning, and, being in accordance with the general 15 rule, need not be wired. Some exceptions which must be wired through one or two connections are:

- (1) Zero suppress in the absence of blanks preceding the field.

- (2) Zero print starting from a predetermined position. 20

- (3) Zero print between two positions.

Another device allows the insertion of the character — (minus) or letters CR (credit), either on the right, or on the left of the quantity to be printed if it is negative. The control of a CR or — on the right of a quantity automatically starts a sign detection. A single connection is sufficient to control the insertion of R, and the C is automatically recorded on its left. In case the quantity is positive, one or two blanks replace — or CR.

During the transfer into the output storage, two connections control an information offset device according to the computed result. The columns in which a quantity (a total, for example) is to be printed may vary according to the sign. A certain number of columns are appointed to a credit balance and different columns to a debit balance. Generally, the debit quantities are printed on the left and the credit on the right, but the contrary is also possible through a single additional connection.

Through a small number of selectors, it is possible to compose differently several successive lines, the splitting, 40 the distribution or the insertions being controlled by miscellaneous conditions acting on the selectors, so that the line format may vary on each edit cycle.

Other objects of the invention will be pointed out in the following description and claims and illustrated in the accompanying drawings, which disclose, by way of examples, the principle of the invention and the best mode, which has been contemplated, of applying that principle.

In the drawings:

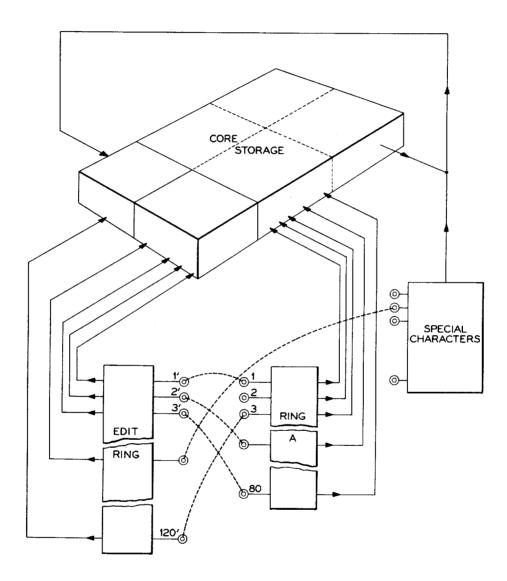

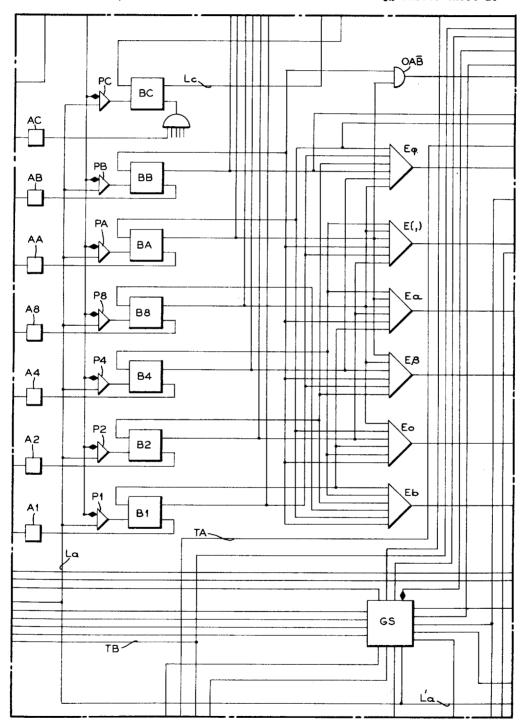

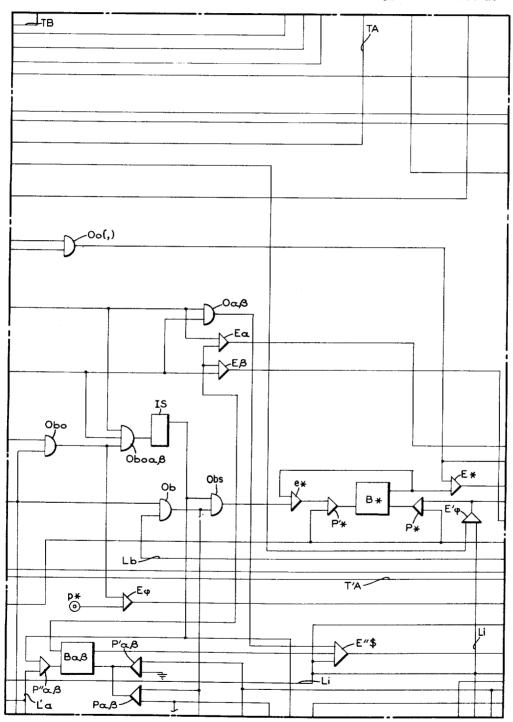

FiG. 1 is a general block diagram of a machine constructed in accordance with the present invention.

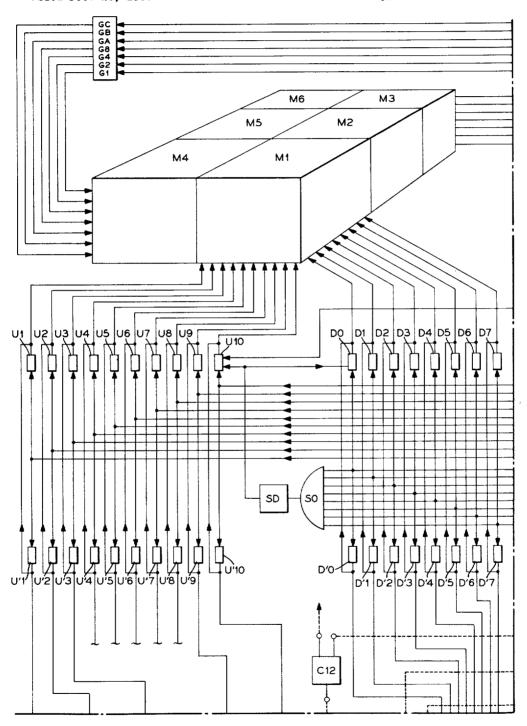

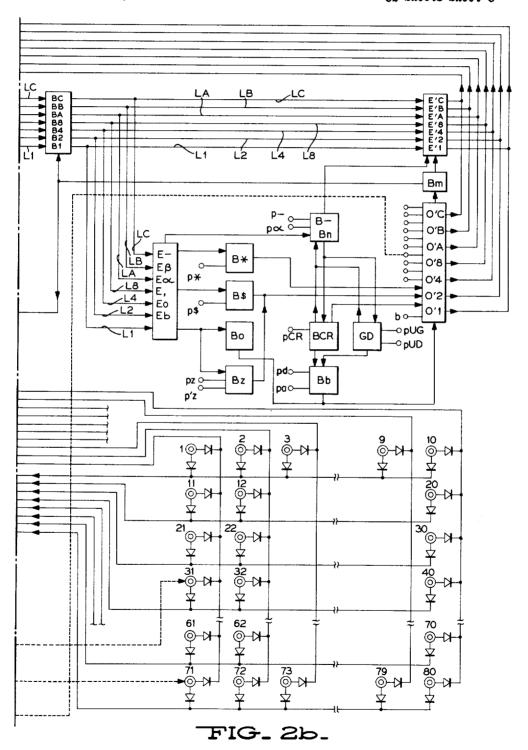

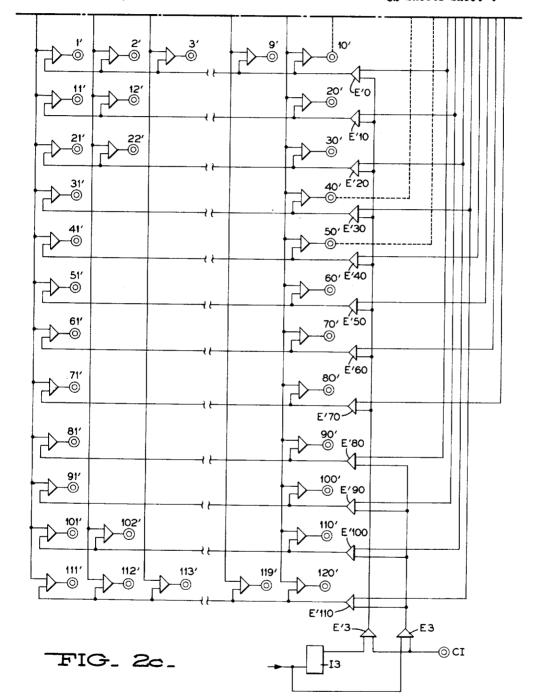

FIGS. 2a through 2c constitute a somewhat more detailed block diagram of the machine as shown in FIG. 1.

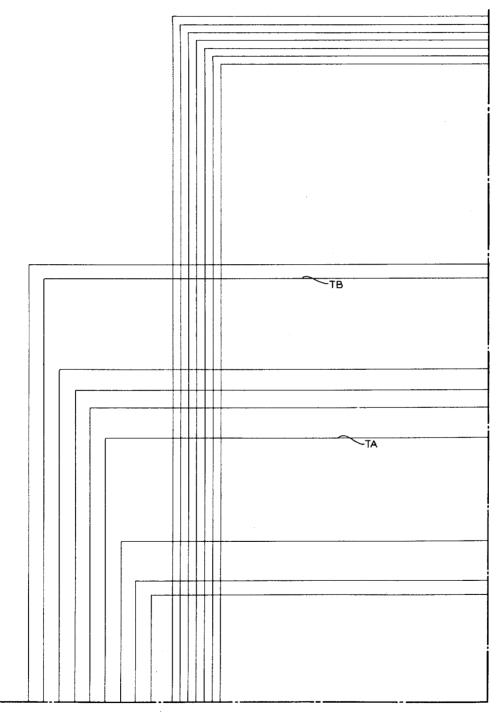

FIG. 3 shows how FIGS. 2a through 2c should be placed together.

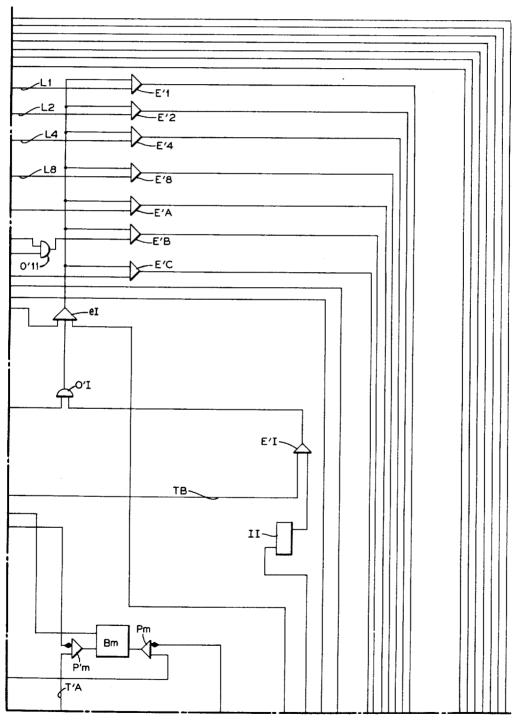

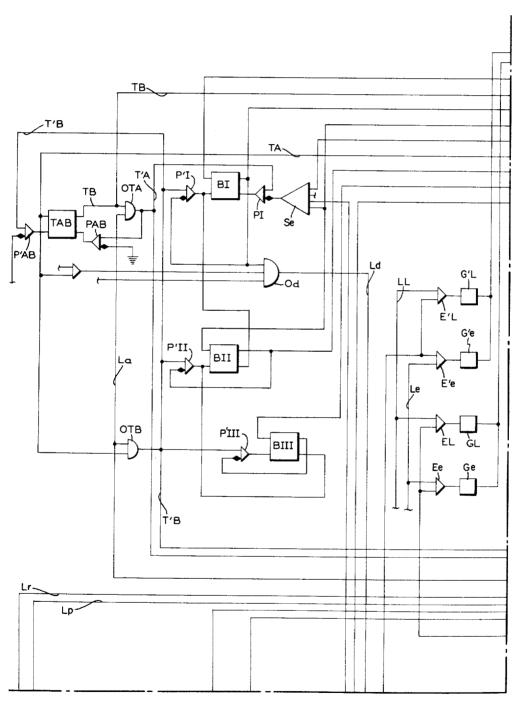

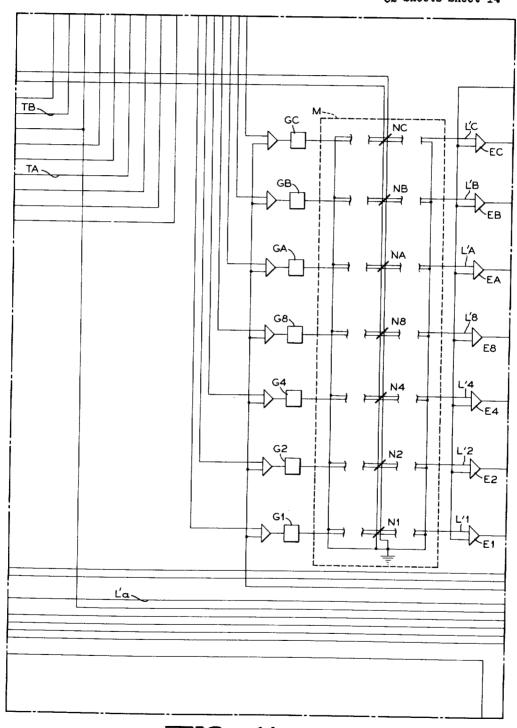

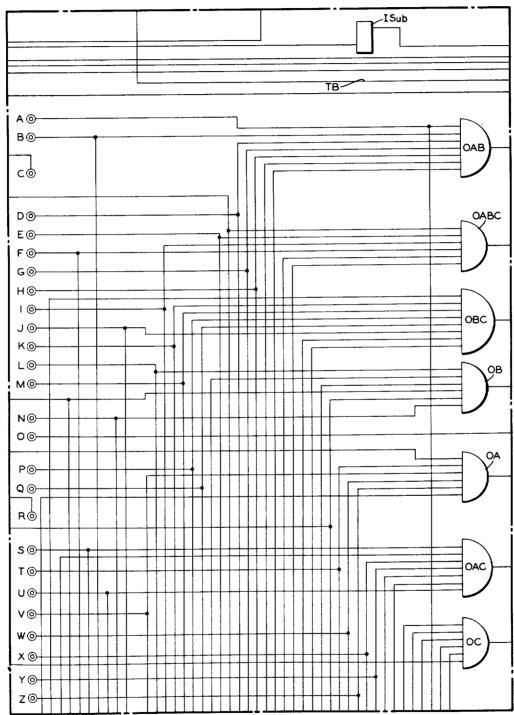

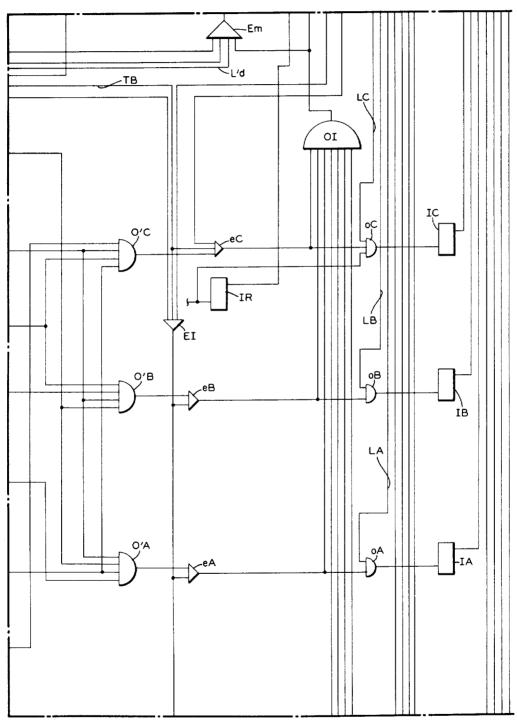

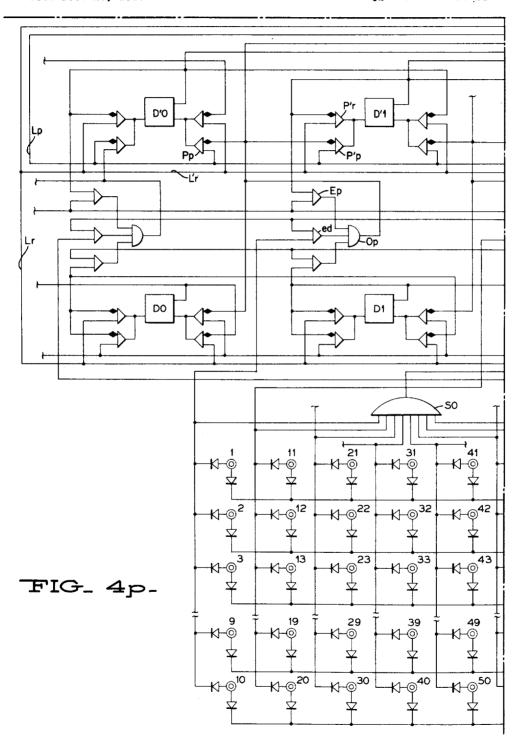

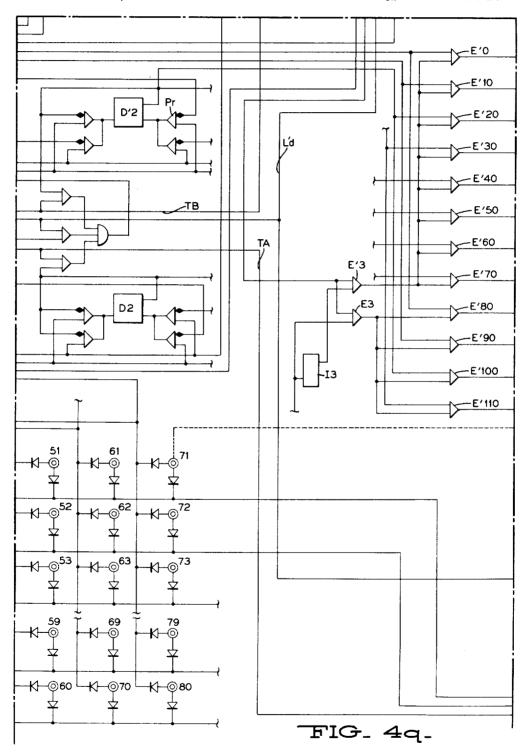

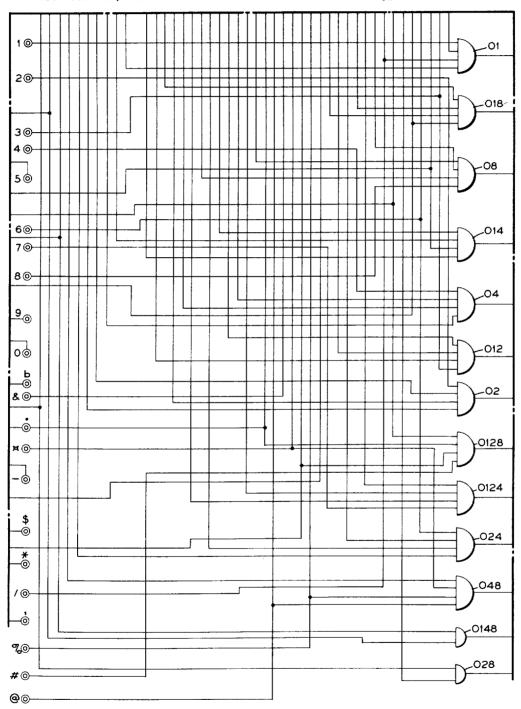

FIGS. 4a through 4x show a detailed block diagram of the machine as shown in FIGS. 2a through 2c.

FIG. 5 shows how FIGS. 4a through 4x should be galaced together.

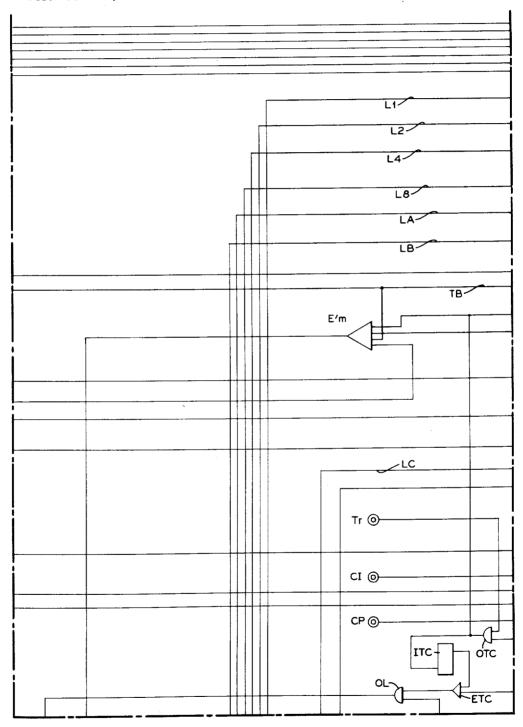

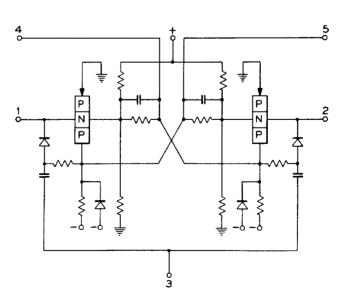

The elementary circuits, symbolically represented in FIGS. 4a through 4x, are explained in the following figures:

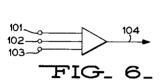

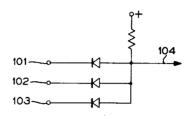

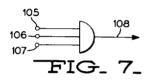

FIGS. 6 and 6a respectively show the symbol and the 65 details of an example of a logical "AND" circuit.

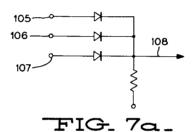

FIGS. 7 and 7a respectively show the symbol and the details of an example of a logical "OR" circuit.

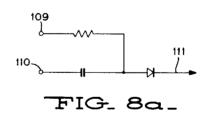

FIGS. 8 and 8a respectively show the symbol and the details of an example of a diode gate.

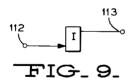

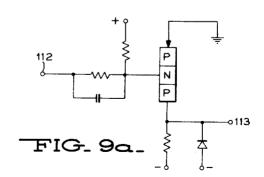

FIGS. 9 and 9a respectively show the symbol and details of an example of an inverter.

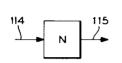

FIGS. 10 and 10a respectively show the symbol and details of a level setter.

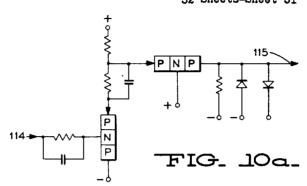

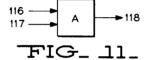

FIGS. 11 and 11a respectively show the symbol and 75 panel.

4

details of a two-input amplifier; FIG. 11b symbolically represents a one-input amplifier.

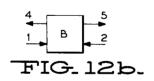

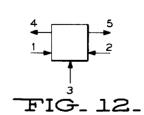

FIGS. 12 and 12a respectively show the symbol and details of a three-input trigger, one being binary; FIG. 12b symbocially represents a two-input trigger.

FIG. 13 shows a machine timing diagram.

#### GENERAL DESCRIPTION—INTRODUCTION

Referring first to FIG. 1, a general block diagram of editing apparatus for a data processing machine is shown. A core storage array is addressed by an edit ring and a second ring shown as Ring A. The edit ring sequentially addresses a fixed group of storage positions in the core storage array to enter data therein. Other positions of core storage are addressed by Ring A from which positions data are read out of core storage and entered back into core storage at the positions addressed by the edit ring. The edit ring has a plurality of exit hubs which are plug wired to control Ring A. Thus as the edit ring advances, Ring A is controlled to address selected positions of core storage.

The edit ring also controls a source of special characters such that the special characters may be inserted in core storage at the positions selected under control of the edit ring.

The edit ring first advances a complete cycle in one direction to transfer data and then advances a complete cycle in the opposite direction to retouch the data transferred.

Referring next to FIGS. 2a through 2c the editing machine will be described functionally in more detail after which the construction and operation of the machine will be described in detail with reference to FIGS. 4a through 4x.

The present machine provides for the composition of an information line to be printed, punched, or in a general way reproduced according to any method. The composition of this information line is performed in a so-called output storage. The information which makes up the line is received from other storages of the machine, a computation operation, or input storage, etc., by a single transfer, but this information is not erased from the storage from which it proceeds; it is immediately regenerated in it, ready for a possible re-utilization. If the storage devices were constructed in such a way that the reading of the information did not erase or destroy it, it would have been unnecessary to re-record. In case the data to be transferred are not located together, the format of the line to be composed is established by a transfer together with a redistribution. The line composition may be completed with insertions or substitutions of informa-

By way of example, the present machine constructs in the output storage the exact picture with all its details of what the operator intends to print, punch or reproduce according to any method. The printing, the punching or the reproduction of the line thus composed is performed in a single operation controlled by a single program. After the printing, for example, blanks are recorded in the output storage, i.e., the C bit which corresponds to a blank is recorded in all the positions of the output storage, and the output storage is then ready to receive the data of the following line.

The content of the output storage is composed during a first direct scanning, during which substitutions, insertions and transfers with or without arrangement may be performed, then retouched during a second scanning in the opposite direction during which only substitutions 70 may take place.

The information line is composed in series, the insertions as well as the rearrangements are performed position by position during a single program controlled electronically through removable connections on the control panel.

-5

The storages are preferably of the low access time type; and, for example, they are shown as made up of a magnetic core array of three dimensions. The magnetic cores may occupy two stable magnetic states marked 0 and 1. The information is recorded in the storages in 5 the form of a seven element code, 1, 2, 4, 8, A, B, C.

According to this code, bits 1, 2, 4, 8 are the binary representation of digits 0 to 9; their combination with information elements A and B are used to represent the non-numerical characters and element C is used to check 10 the parity (the number of information elements used to represent any datum being odd).

The magnetic cores may be assembled in any manner, for example in various storage groups; each one of these groups being composed of 80 distinct positions, and each 15 position capable of storing any of the characters. To each position correspond 7 magnetic cores, so that a group, including for example 80 positions would be made up of 80×7 or 560 magnetic cores. Each one of the seven cores corresponds to one of the seven bits 1, 2, 4, 8, 20 A, B, and C. The complete machine could, for instance, include 5 storage groups, and the part reserved for the output storage could comprise one, one and a half or two groups, i.e., it would allow the composition of a line of 80, 120 or 160 characters. According to the ex- 25 ample shown in FIG. 2a, the storage is made up of groups M1, M2, M3, M4, M5 and M6. For example, each one of blocks M3 and M6 may include 40 positions, the others including twice as many. So that, according to this example the storage as a whole would 30 comprise 400 positions arranged in a square of 20 by 20.

If the output storage is made up of groups M2 and M3, the composed line would thus include 120 characters,

All the positions of a storage group may be determined by two scanning devices: readout (A) and read-in 35 (B), distributing distinct pulses A and B to scan respectively two areas A and B of the storage. Both areas A and B may be in the same group or in two distinct groups. Each one of these pulse distributing devices A and B may be made up of chain comprising a certain number of trigger stages (80, for example), as shown in our copending application Serial No. 643,369, filed March 1, 1957, or of the combination of two chains, one including m triggers marked as units (for example, m=10 from 1 to 10) and the other including n triggers marked as tens (for example, n=8 from 0 to 7) their combination allowing also to define 80 stages. According to the first example, each trigger stage is associated with the 7 magnetic cores of a position of the storage, and consequently determines the 7 information elements of the datum recorded in said position of the storage. When the trigger of a stage is "on," a datum may be either read or recorded into the 7 magnetic cores of the corresponding storage position. According to the second example, the combination of a tens trigger and of a unit trigger take the same part in determining a position of the storage. This example is shown in FIG. 2a; the triggers are marked U1, U2, U3, U4, U5, U6, U7, U8, U9 and U10 in the units chain of device A and U'1, U'2, U'3, U'4, U'5, U'6, U'7, U'8, U'9 and U'10 in the units chain of device B; D0, D1, D2, D3, D4, D5, D6 and D7 in the tens chain of device A and D'0, D'1, D'2, D'3, D'4, D'5, D'6 and D'7 in the tens chain of device B. The "on" state of triggers U4 and D6, for example, allows, during time A, the selection of position 64 of the storage; it is then possible to read or to record in it the 7 information elements of a

The scanning chains thus mark the positions of a storage group. The choice of the storage group is selected through two so-called group selection chains including as many triggers as there are groups. Such chains are shown and described in our copending application (Docket 5588). The group selection chains are not shown in the figures.

For each one of the scanning chains, all the stages are 75 for the recording. Then, the 7 triggers of the register

6

"off" except one which is "on"; an advance pulse resets this stage and starts the following stage. Once the chain has started, its progression is automatic; it thus scans an area of the storage. Both devices A and B are interdependent. In its turn, each one of them progresses one stage to read or to record alternatively the 7 information elements making up a digit or a letter of a number, or a word of an A area, the elements of another digit (or letter) of the number or word of the B area, then those of the following digit (or letter) of A, and those of the following digit (or letter) of B, and so on.

Due to the difference in time of the advance pulses of pulse distributing devices A and B, their combination scans respectively two storage areas position by position, and thus allows the reading, one by one, of the data recorded in a determined area A and to record them in a second area B, to thus transfer the information from area A to area B.

The successive progression of both scanning devices A and B determines two times of operation, readout or A, and read-in or B. These two times overlap so that while a scanning chain is determining an address of the storage, the other chain progresses one stage and vice-versa.

Each one of these times A and B is subdivised into a certain number of elementary times for the reset, reading, checking, recording, etc. After the reading and recording in the storage position corresponding to the "on" stage of scanning device A, the reading and recording in the position corresponding to the "on" stage of device B takes place.

Each one of the 80 positions of a storage group corresponds to an input terminal common to both scanning devices A and B. These 80 terminals are marked 1, 2, 3, 4, ... 79, 80; in FIG. 2b. One of these terminals, either in device A or in device B, puts the triggers of the stage on from which it is desired that the device starts. Hence, said terminal allows the reading and recording from the position corresponding to this stage. For example, a pulse arriving on terminal 31, allows the switching of the tens triggers D3 and D'3 of scanning chains A and B, and the switching of units triggers U1 and U'1. Let us assume that this starting pulse appears during a time A; only triggers D3 and U1 of both scanning chains A will switch on. The coincidence of on state of D3 and U1 determines position 31 of the selected storage group.

In the position determined by scanning device A, the 7 information storage elements read out of during the portion of time A reserved for reading are stored in a 7 trigger register B1, B2, B4, B8, BA, BB and BC which switch on or stay off according to whether the magnetic cores in the respective positions were in saturation state 1 or 0. The reading of the information contained in the cores occurs simultaneously with its erasing, and those of the 7 cores of the position read by scanning device A, which were in state 1, switch to saturation state 0, the others remaining in state 0. While scanning device A always determines the same address in the storage during the recording time, the information received at the output terminals of the 7 trigger register is regenerated in the same position of the storage over lines L1, L2, L4, L8, LA, LB and LC, of the regenerating device E'1, E'2, E'4, E'8, E'A, E'B and E'C under control of recording pulse generators G1, G2, G4, G8, GA, GB and GC. The trigger register is not reset, but retains the information read in time A during the following time B. Scanning device B determines a new position of the storage; the reading of the information elements stored in this position occurs simultaneously with their erasing, but they are not recorded in the trigger register. On the other hand by following the same way as previous, from lines L1, L2, L4, L8, LA, LB and LC to generators G1, G2, G4, G8, GA, GB and GC, the information which was contained in register B1, B2, B4, B8, BA, BB and BC is transferred in this new position during the portion of time B reserved

are reset and the operation resumes, thus allowing the transfer of the information from the successive positions of an A storage area to the positions of another B area, while retaining it in the first area. The information transfer from one area to another may be according to our copending application (Docket 5588).

The B storage area covers all the positions of the line to be composed; it makes up the output storage; the information which is accumulated in it is the picture of the line to be reproduced and controls the output, printing, 10 punching, etc. device.

According to the example shown in FIGURES 2a, 2b and 2c, the line to be edited comprises 120 characters (a blank being considered as a character). Therefore, it is necessary to gather the whole information within two 15 groups of memories, one having 80 positions and the other 40 positions; for clearness sake, let it be assumed that the groups M2 and M3 make up the output memory. The accumulation of the 120 character information bits is performed serially, that is successively one character after 20 the other; therefore device B is to scan in turn all the 120 positions of the output memory. The scanning device successively produces 120 pulses permitting to determine the 120 corresponding positions of the output memory. Such synchronism between the emitted pulse and the position reached is used to control the editing of a line, as will be explained further. Such pulses are available at output terminals referred as 1', 2', 3', . . . 119' and 120'. Some such terminals have been represented in FIGURE 2c. For example, the signal from the tens trigger D'6 is combined with the signal from unit trigger U'1 to produce output pulse 61 from scanning device B and to appear at the pulse emitting terminal indicated as 61' synchronously with the scanning of location 61 in memory group M2. The 40 pulses corresponding to the 40 locations of 35 memory group M3 are available at terminals 81' to 120' the latter can emit pulses but if the logical "AND" circuits, designated by E'80, E'90, E'100 and E'110, have one input favored by the output signal from logical "AND" circuit E3. Such signal exists but if the controlled 40 program is a print edit operation (terminal CI being energized) and if a pulse indicating that the data are to be stored in memory group M3 occurs simultaneously at the input of inverter I3. When there is no pulse at the input of inverter I3, there is a signal at the output of I3 45 which manifests that the 80 locations of memory group M2 are being scanned, and this signal favors logical "AND" circuit E'3 which in turn favors logical "AND" circuits E'0, E'10, E'20, E'30, E'40, E'50, E'60 and E'70 which favors the 80 logical "AND" circuits associated 50 with the 80 emitting terminals 1' to 80'. These 120 terminals emit pulses but if the cabled program comprises an editing operation, the print edit terminal designated by CI is energized which favors either the 80 logical "AND' circuits associated with the 80 output terminals 1' to 80', 55 or the 40 circuits associated to terminals 81' to 120'.

During each operation time B, the information transfer from register B1, B2, B4, B8, BA, BB, BC to the output memory position defined by the scanning device B is performed while remaining under the control of the plugboard and more precisely under the control of the series of 120 pulses emitted by scanning device B at the output terminals L' to 120'. These pulses redistribute the information coming from the working memory according to any order, or to effect any print edit operation: inserting 65 one or more characters, such as floating dollar, check protection asterisk, blank, zeros suppress, maintaining zeros, offset or CR insertion according to the sign.

To control a redistribution of the information it is sufficient to connect one of the 120 output terminals of scan- 70 ning device B with one input terminal. For example, let it be assumed that the connection shown in dotted lines in FIGURES 2a, 2b and 2c is realized between the emitting terminal 40' and the receiving terminal 71. The

til the scanning device B senses position 40 of the output memory, i.e., triggers D'3 and U'10 are "on." At that moment, the pulse emitted from terminal 40' is applied through the flexible connection to terminal 71, runs through logical "OR" circuit SO to energize the skipping device SD which stops the scanning chains A in the storage position reached and restarts them from position 71, that is, triggers D7 and U1 are switched "on." This skip of the scanning chains A, under the control of scanning chains B redistributes the transferred information according to any predetermined order. In case it would be desired, this skipping may be simultaneous with a change of memory group, i.e., if, after transferring the information coming from some positions of a memory group, the operator desires to transfer the information coming from another group, the same pulse produced by the scanning device B simultaneously controls chains A restarting from the stage corresponding to the new desired position, and at the same time controls the change from one memory group to the other. This double control may be effected through a circuit C12 having one input and two outputs, such as that shown in FIGURE 2a. According to the represented example, an input of this circuit C12 is connected to the emitting terminal 10' and receives a signal when the chains B sense position 10; a first output signal is applied to the receiving terminal 31 and permits chains A to restart from stage D3 and U1 while a second output signal from circuit C12 control the change of memory groups. Such control may be as shown in our abovementioned copending application (Docket 5588).

It is obvious that such circuits could be generalized and that the number of output signals could be increased. One might utilize for example such a circuit as an input signal produces 3 or more output signals if it is desired to control a sign detection for instance, or any other machine function, besides chains A skip and memory groups change.

The 120 output terminals of scanning device B emit pulses controlling the various functions of the editing machine. For example, let it be assumed that the operator wants to insert letter Z in position 50 of the line being edited; it will be sufficient to connect terminal 50' to terminal Z of the inserting device O'1, O'2, O'4, O'8, O'A, O'B and O'C. This connection is shown in dotted lines in FIGS. 2a, 2b and 2c. When scanning device B senses position 50, triggers D'4 and U'10 are switched "on"; a pulse appears at terminal 50' and is applied to terminal Z of the inserting device. The latter translates letter Z according to the seven bit code (thus code corresponding to letter Z is 1, 8 and A) and by means of pulse generators G1, G2, G4, G8, GA, GB and GC records such bits into the memory position 50 determined by scanning chains B. Further, such inserting device enables the following by means of hold trigger Bm:

(1) To stop the information transfer from area A to area B, because hold trigger Bm prevents the regeneration device E'1, E'2, E'4, E'8, E'A, E'B and E'C from being favored and this switches off the transfer circuit.

(2) Trigger Bm is effective in preventing register triggers B1, B2, B4, B8, BA, BB and BC from being reset, thus the information which is to be kept and recorded in the position following that where character Z has been recorded, is not erased from the register.

(3) Trigger Bm stops the advance of the scanning chains A.

Hold trigger Bm fulfills these three functions whatever may be the character to be inserted and as long as there are characters to be inserted.

The inserting device O'1, O'2, O'4, O'8, O'A, O'B and O'C permits the insertion of all letters, digits or special character, such as: % . & , /.

The position wherein an insertion is taking place may be chosen at random. It may also be automatically determined in accordance with the quantity to be registered, transfer of the information will normally be effected un- 75 for example when it is desired to insert the floating dollar,

The insertion of a character may be conditional or not; it is conditional for instance when character - is only to be inserted if the quantity to be printed is negative; if the quantity is positive, a blank is to be recorded instead.

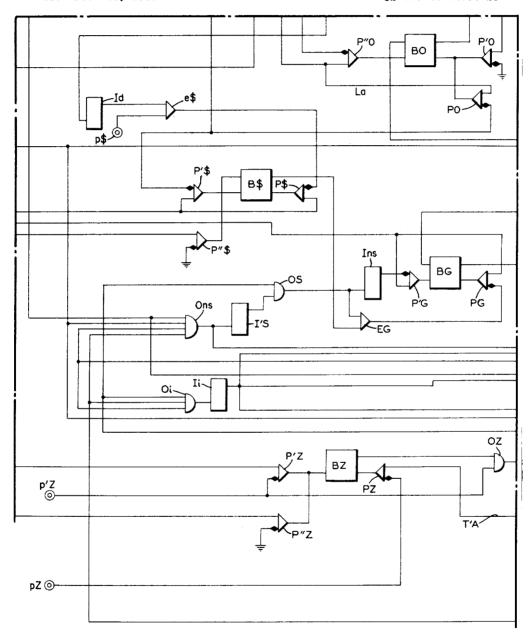

The machine comprises special code detecting devices Eb, Eo, E(,), E $\alpha$ , E $\beta$ , E-, . . . which, connected to the output of triggers B1, B2, B4, B8, BA, BB and BC of 10the register, are operative in detecting the existence of bits corresponding to a blank, a zero, a comma,  $\alpha$ ,  $\beta$ , a minus (-). Besides it comprises a sign detecting device called B- Bn. On the plugboard, terminal p- may be connected to one or more of the 120 output terminals 15 of the scanning device B. When the corresponding position in the output memory is reached, the pulse emitted by said terminal is applied to p- and starts a sign detecting operation, i.e., that the sign of the quantity is registered in trigger B-. Further, via regeneration device 20 E'A, E'B and E'C, trigger Bn erases bits A and B that could cause an error to be made by translating a number as a letter and corrects bit C according to the parity of the number of bits that might have been changed when bits A and B were suppressed. The operation of Bn, that 25 is, the numerical interpretation of all the data is carried on until a position is reached whose corresponding emitting terminal is connected to  $p\alpha$ . From this position the numerical interpretation is interrupted and the alphanumerical interpretation is resumed.

The check protection asterisk inserting device B\* and floating dollar inserting device B\$ are controlled by terminals p\* and p\$, respectively, which receive the pulses emitted by the 120 terminals of the scanning device B.

The zero suppress device Bo erases zeros placed left of 35 the first significant digit, and is controlled by the code detecting device, and more specifically by the zero detecting circuit Eo, the comma detecting device E(,), and the blank detecting device Eb. The Bo device is automatic, i.e., it works for all 120 positions of the output memory and therefore on the plugboard no input terminal corresponds to this device since it is useless to connect it to any of the emitting terminals. During the reverse scanning it allows the substitution of blanks for all zeros and commas on the left of the first significant digit.

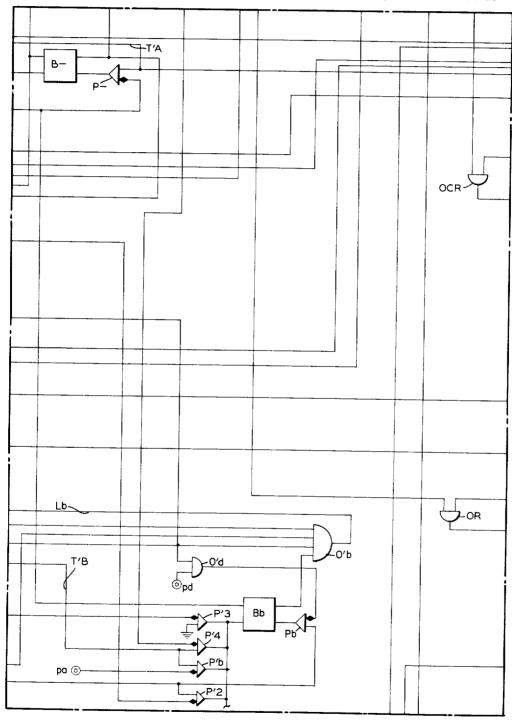

The zero print device BZ allows zeros to be retained and recorded in the output memory between two positions according to the operator choice. The output terminals of scanning device B corresponding to these two positions must be connected in the plugboard with terminal pZ and p'Z. Such device replaces bits 2, 8 and C which represent a zero by bit A, which represents a significant zero.

A blank inserting device Bb allows the insertion of a blank in a given position or a series of adjacent blanks between two given positions, or blanks under the control of 55 an inhibiting magnetic field other devices. The insertion of a single blank is controlled by means of terminal b, as was the insertion of other special characters. Inserting a series of blanks is controlled by means of two terminals pd and pa which are available on the plugboard and may receive pulses emitted  $^{60}$ by the output terminals of the scanning device B so as to determine the start and stop positions between which these blanks are to be inserted. Blank insertion is effected with priority on any other insertion.

The CR inserting device (CR being the first letters of  $^{65}$ the word "Credit") designated by BCR controls, through circuits O'1, O'2, O'4, O'3, O'A, O'B and O'C, the insertion of CR into the next position to the right or to the left of a quantity if said quantity is negative, and it controls the insertion of blanks instead of letters CR if such 70 quantity is positive. In a similar way, the offset device called GD allows the printing of positive quantities in a number of positions while the negative quantities are printed to the right to these positions so as to align quanti-

are to be inserted in the positions assigned to the negative quantities, and conversely. Thus, the blank inserting device Bb may be controlled by the devices BCR or GD wherewith it is connected. Besides insertion of CR and offset depending on the sign of the quantity, devices BCR and GD are related to the sign detecting device B- to initiate the recording of the sign; then in turn, B- controls the insertion of CR or of blanks and a right or left

All the functions briefly mentioned through this chapter will be further described in special chapters. Only the general principles of the machine operation has been described with reference to FIGS. 2a, 2b and 2c; the description of the various machine devices will be described with reference to the detailed FIGS. 4a through 4x, wherein, for clearness sake, the same organs will be designated by the same references as in FIGS. 2a, 2b and 2c.

The characteristics of all the basic elements of the machine: control, scanning, synchronization signal generators, arrangement of scanning chains, storage component circuits, storage field definition have been described with more details in copending applications: Serial No. 643,369, Filed March 1, 1957 (chains); Docket 5544 (input); Docket 5588 (field definition). It will be advisable to refer thereto for a better understanding of the explanation below.

### INFORMATION TRANSFER

The basic print or punch editing operation is the transfer of a datum recorded in a given storage A field into a B field of the output storage. These fields A and B are defined through scanning devices A and B according to the method described in the copending application (Docket 5588). Let us assume that field A extends from start position d to stop position a and that field B extend from d' to a'. Scanning devices A and B start respectively at the stages of the triggers corresponding to positions d and d', i.e., in chains A and B, the "tens" triggers and the "unit" triggers, which define positions d and d' switch "on." The output signals of said triggers allow, during the reading, the generation of a magnetic field

$$-\frac{H}{2} - \frac{H}{2} = -H$$

45 in the seven cores of position d; said field produces a read signal on lines L'1, L'2, L'4, L'8, L'A, L'B and L'C (FIG. 4i) corresponding to the cores which occupied saturation state 1 and bring said cores back to state 0. During the recording, these triggers allow the generation in these 50 7 cores of a magnetic field

$$+\frac{H}{2}+\frac{H}{2}=H$$

which switches to saturation state 1 the cores in which

$$-\frac{H}{2}$$

is not produced. During time A, the reset pulse applied to the left inputs of triggers B1, B2, B4, B8, BA, BB and BC (FIG. 4j) of the register switch them "off." Then a read pulse goes through the windings of the 7 magnetic cores of position d. The information read in these cores appear on the 7 lines L'1, L'2, L'4, L'8, L'A, L'B and L'C; the existence or the absence of signal on these lines corresponds to saturation state 1 or  $\overline{0}$  of the 7 cores. The read signals go through logical "AND" circuits E1, E2, E4, E3, EA, EB, EC (FIG. 4i) (the second input of which is favored, during time A, by a signal from logical "OR" circuit OL (FIG. 4b), read amplifiers A1, A2, A4, A8, AA, AB and AC, and are applied to the right input of triggers B1, B2, B4, B8, BA, BB and BC (FIG. 4j). These 7 triggers make up the register where is kept the information read out of position d of the storage; the ties having same sign; if the quantity is positive, blanks 75 signal appearing on the right outputs of the 7 trigger

register makes up the picture of the information which has just been read.

In order to avoid losing this information, which may be reused, it is regenerated in the same position d of the storage. For this, through lines L1, L2, L4, L8, LA, LB and LC, the right outputs of the register's triggers are connected to logical "AND" circuits E'1, E'2, E'4, E'8, E'A, E'B and E'C (FIG. 4g). The second input of these "AND" circuits is favored during time A by a signal from logical "OR" circuit O'I then from logical "AND" circuit el. The signals from the register consequently go through logical "AND" circuits E'1, E'2, E'4, E'8, E'A, E'B and E'C, then logical "OR" circuits O1, O2, O4, O8, OA, OB and OC (FIGS. 40 and 4x), and are applied to the inputs of inverters I1, I2, I4, I8, IA, IB and 15 IC. For each of information elements 1, 2, 4, 8, A, B, C to be recorded, there is signal at the input of the corresponding inverter, hence no output signal. The output signals of said inverters are applied to inhibition current pulse generators or inhibition core drivers G1, G2, G4, G8, GA, GB and GC (FIG. 4i) which respectively generate, in the windings of all the magnetic cores of the storage located on corresponding line 1, 2, 4, 8, A, B or C, inhibition magnetic fields

$$-\frac{H}{2}$$

such that the presence of an inhibiting field in a core prevents said core from switching from saturation state 0 to state 1. In the 7 cores of position d of the storage determined by a tens trigger and a unit trigger of scanning chains A, these triggers allow the generation of magnetic fields

$$+\frac{H}{2}+\frac{H}{2}=+H$$

In those of the 7 cores for which no signal is to be recorded, an inhibiting field

$$-\frac{H}{2}$$

is generated which holds the core in remnant state 0, since the total of magnetic field

$$\frac{H}{2} + \frac{H}{2} - \frac{H}{2}$$

or

$$\frac{H}{2}$$

is not sufficient to switch the core to saturation state 1. On the contrary for those of the 7 cores in which a signal is to be recorded, there appears no output signal from the corresponding inverter, and the pulse generator generates no inhibiting field; consequently, the corresponding core undergoes a magnetic field

$$\frac{H}{2} + \frac{H}{2}$$

or H sufficient to switch it from saturation state 0 to

It is obvious that, if the storage had been made up of magnetic cores such that the reading of the recorded information does not occur simultaneously with its erasing it would have been unnecessary to record it again.

At the end of the first time A, the 7 bits which were present in position d have been read out written in the trigger register, and rerecorded in the same storage position. During time B, these bits are recorded in position d' determined by the tens triggers and unit triggers of scanning chains B. During time B, no reset pulse favors the slow input of diode gates P1, P2, P4, P8, PA, PB and PC (FIG. 4j); consequently, the 7 triggers B1, B2, B4, B8, BA, BB and BC of the register are not reset and the information read during the preceding time is held in it.

12

determine position d' of the storage, and allow the generation in the read windings of the 7 cores of position d'magnetic fields

$$-\frac{H}{2}-\frac{H}{2}$$

or -H. These magnetic fields switch back to saturation state 0 those among the 7 cores which were in state 1 and, by erasing the information which was recorded in them. allow it to be replaced with the information to be transferred. The read signals corresponding to these cores will appear on lines L'1, L'2, L'4, L'8, L'A, L'B and L'C (FIG. 4i) and will be applied to an input of logical "AND" circuits E1, E2, E4, E8, EA, EB and EC, but since these signals are not desired, they do not go through these circuits because the second input of said circuits is not favored during time B. As a matter of fact, if the controlled program is "transfer," "print edit" or "punch edit," a signal will appear on one of the three terminals Tr, CI, or Cp (FIG. 4b), hence on the output of logical "OR" circuit OTC, that is, on the input of inverter ITC. There will be no signal on the output of ITC nor to one of the inputs of logical "AND" circuit ETC; circuits E1, E2, E4, E8, EA, EB and EC (FIG. 4i) 25 are not favored and the information read in position d' is thus ignored; it is not applied to amplifiers A1, A2, A4, A8, AA, AB and AC nor to triggers B1, B2, B4, B8, BA, BB and BC (FIG. 4j) of the register. Thus during time B, the information appearing on the register's output is still that which was read during time A; it is this information which is recorded in position d' of the storage. As previously explained for the rerecording in position d. the read signal follows the same way: it goes through logical "AND" circuits E'1, E'2, E'4, E'8, E'A, E'B and E'C (FIG. 4g), logical "OR" circuits O1, O2, O4, O8, OA, OB and OC (FIGS. 40 and 4x) and is applied to the inputs of inverters I1, I2, I4, I8, IA, IB and IC, then to inhibiting current pulse generators G1, G2, G4, G8, GA, GB and GC (FIG. 4i) but now, during the recording time, the 7 cores of position d' are the ones which are determined by scanning chains B. The windings of these 7 cores consequently receive the recording currents which generate magnetic fields

$$\frac{H}{2} + \frac{H}{2}$$

and which respectively proceed from the tens trigger and the units trigger of chain B. For those among the 7 cores of this position d' in which no bit is to be recorded, the inhibition generators induce magnetic fields

$$-\frac{H}{2}$$

which hold them in remnant state 0, while in those in which an information element is to be recorded, the absence of a signal on the output of the inverters corresponds to the absence of the inhibiting field, and these cores switch to saturation state 1.

All the digits, letters and special characters are translated into a code which allows the initiation of them in the storage with a certain number of bits chosen among 1, 2, 4, 8, A, B, C so that this number be odd; this has the advantage to allow, during any period of machine operation, the detection of an error, making it certain that the number of bits representing any character is not even. All the errors leading to a change of parity of this number will be detected, either those caused by the absence of a bit which should have been present, or those caused by the existence of a bit which should have been absent, whether this error concerns one bit or any odd number of bits. This parity check may be performed according to any well known method. It is possible, for instance, to determine whether the number of bits, during the recording of the character in the storage is compatible according to parity. This parity check may, for in-A tens trigger and a unit trigger of scanning chains B 75 stance, be performed at the level of logical "OR" circuits

O1, O2, O4, O8, OA, OB and OC and inverters I1, I2, 14, 18, IA, IB and IC.

At the end of the first cycle A and first cycle B, the information has been transferred from the storage position d to position d', while being regenerated in position 5 d; the following cycle begins with a reset of the 7 trigger register, through diode gates P1, P2, P4, P8, PA, PB and PC (FIG. 4j). The register is now ready to receive the information read out of the following position determines as an address, position (d-1) of the storage; the information read out of this position is first written in the register then recorded again in position (d-1). Chain B progresses one stage and determines position (d'-1); the information read out of this position is left 15 aside and, in its place, is written the information contained in the register, i.e., that read from (d-1).

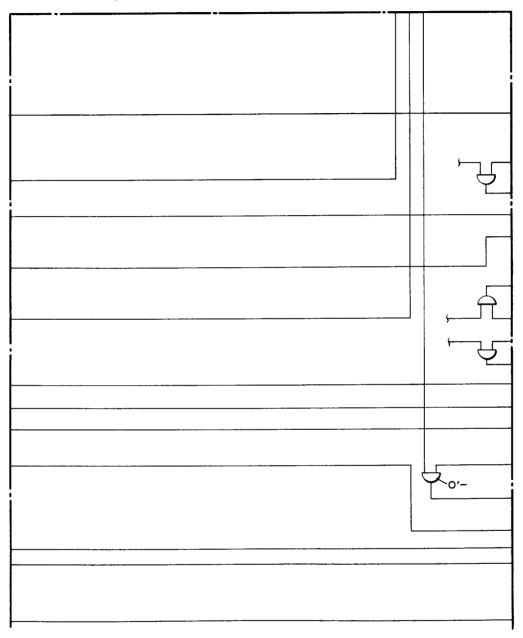

Chains A and B keep up this progression and the transfer from one field to the other continues for all the successive positions, the information accumulating in 20 field B, i.e., in the output storage, until chains B have scanned all 120 positions of the output storage; then they stop, thus causing scanning chains A to stop and the transfer to end.

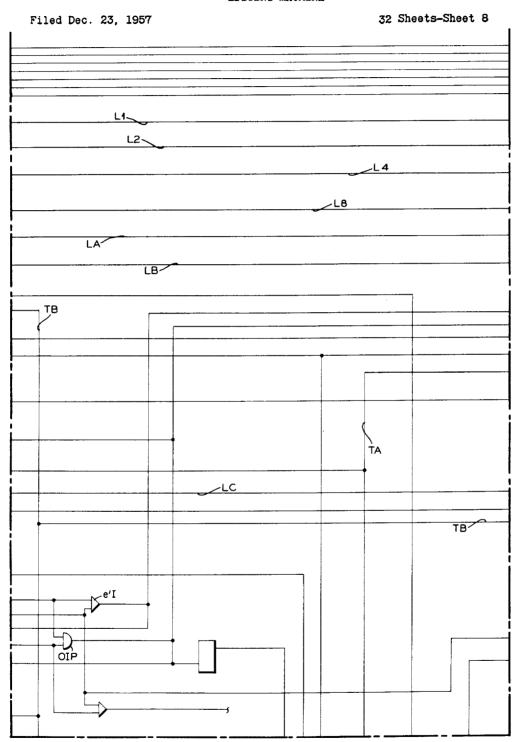

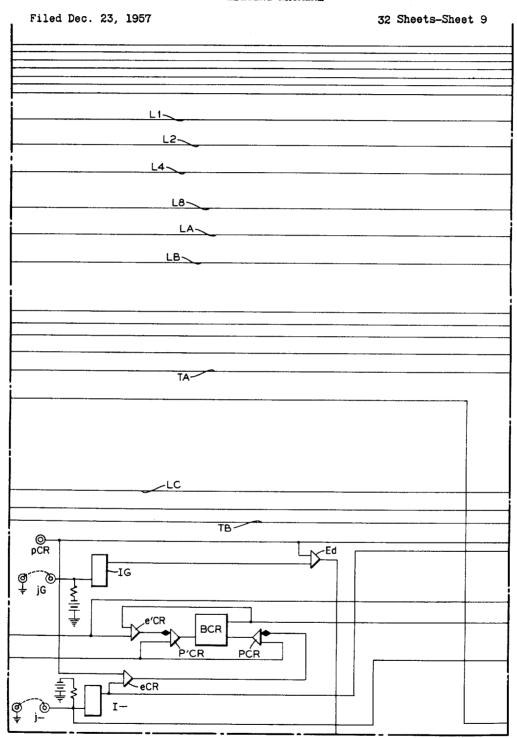

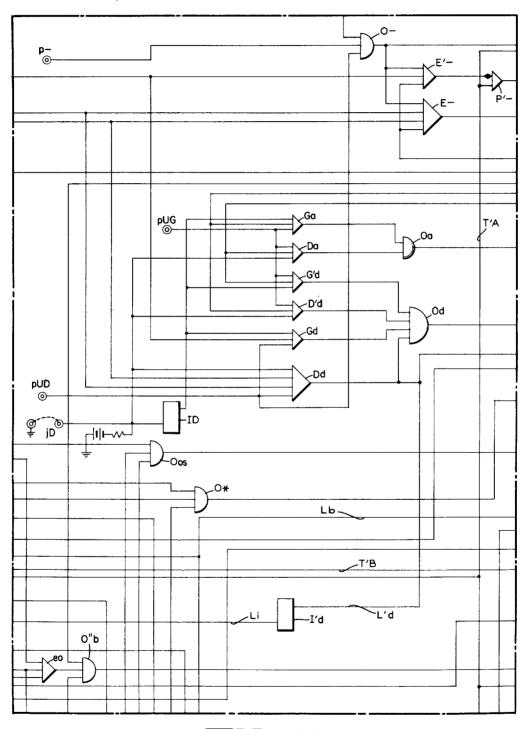

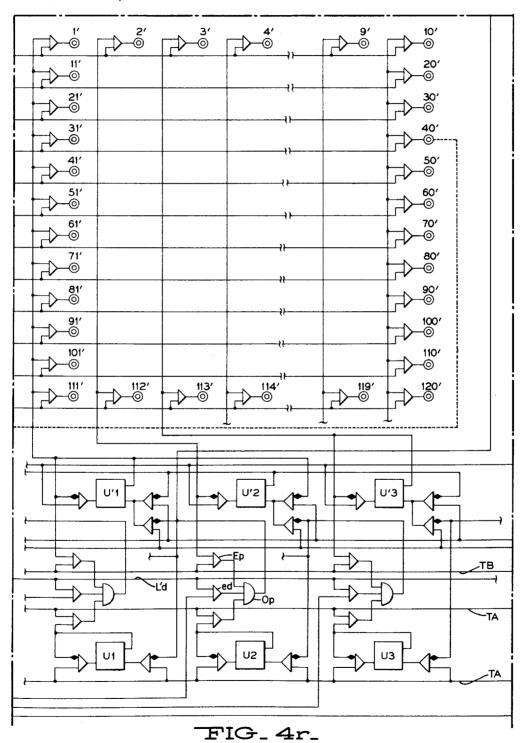

In FIGS. 4p, 4q and 4r, scanning device A has been 25 represented by three tens stages: triggers D0, D1 and D2, and by three unit stages: triggers U1, U2 and U3 as well as the connecting circuits between said triggers; scanning device B has been represented by three tens triggers: D'0, D'1 and D'2 and three unit triggers U'1, 30 U'2 and U'3. It is quite obvious that the other triggers which are not shown, D3 to D7, U4 to U10, D'3 to D'7 and U'4 to U'10 as well as their interconnecting circuits, may be made up the same way. Some of input terminals 1, 2, 3, ... 89 common to chains A and B, as well 35 as some of output terminals 1', 2', 3', . . . 120' of B have been represented (FIGS. 4p, 4q and 4r), arranged and marked as in FIGS. 2b and 2c.

Output terminals 1' to 120' represented in FIG. 4r of scanning device B receive the output pulses only if the 40controlled program is a print edit, i.e., if terminal CI is energized. Other output terminals, which are not shown in the figures, would allow to receive the output signals from scanning device B if the controlled program were the editing of an information line to be  $^{\,45}$ punched, i.e., if it is terminal Cp which is energized. In print edit as well as in punch edit, the output terminals emit pulses synchronized with the position of the storage reached by the scanning, and allow to control any change in the information transfer toward this position. The 50signals from these terminals are eliminated during operating time of skip trigger BIII, in order to avoid that one of the signals, after controlling a skip, be wrongly interpreted. For this, the left output of BIII (FIG. 4h) is wired to an input of logical "AND" circuit e'I (FIG. 4c) which may be favored only if BIII is off. Print edit control terminal CI is wired to the second input of e'I. The signal on the output of e'I allows to favor either logical "AND" circuit E'3 and the 80 logical "AND" circuits associated with the 80 output terminals 1' to 80' 60 or logical "AND" circuit E3 and the 40 logical "AND" circuits associated with terminals 81' to 120', whether that data is to be recorded in storage group M2 or M3, i.e., whether a signal appears on the output or the input of inverter 13.

The starting of the scanning devices, i.e., the switching on of a tens and of a unit trigger of device A or B, is performed through logical "AND" circuits ed (FIG. 4p) an input of which is favored by a start pulse proceeding through line Ld and the other input by the terminals 1 to 80, which corresponds to this stage. The start signal proceeding from "AND" circuit ed goes through "OR" logical circuit Op in order to energize diode gates Pp and switch "on" the triggers of the determined

14

The progression in forward direction of device B (FIG. 4p), for example, is performed from right to left, i.e., from 80 to 1, successively from the right output of the on trigger through logical "AND" circuits Ep (an input of which is favored during time B through line TB) "OR" logical circuits Op, diode gates P'p to reset the trigger which is on, and Pp to switch the trigger on its left on. The progression takes place according to a similar principle in the tens and unit chains of scanning de-(d-1). Scanning chain A progresses one stage and 10 vices A and B, on each one of the corresponding progression pulses applied by lines Lp.

The scanning is performed in backward direction from 1 to 80, when the progression pulses appear no longer on line Lp and so called regression pulses appears on lines Lr; through diode gate P'r, the signal on the right output of the trigger on resets it, and through Pr it switches the following trigger on the right on.

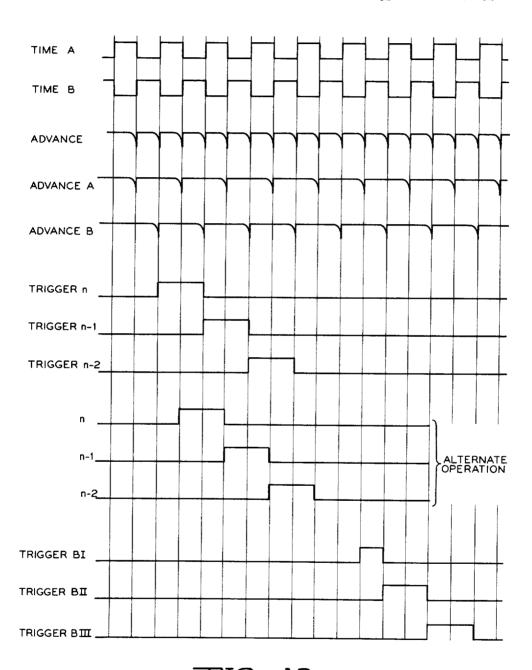

Both operating times A and B are determined through trigger TAB, FIG. 4b. On the left output and on the right output of the trigger appear complementary signals shown in the time diagram, FIG. 13, time A corresponding to the left output (trigger TAB on); the signals determining times A and B are respectively applied on lines TA and TB.

Generator Gs comprises several triggers and allows to generate all synchronization and progression pulses necessary for the operation of the machine and of the print edit device in particular. Such a generator is described in the above-mentioned copending applications (Dockets 5544 and 5588), which determines elementary times which subdivise above-mentioned times A and B and which may be used in succession to synchronize, for example, the reset of the triggers, the reading of the storage information, the checking, the production of delay pulses, the recording of the information or any other function. Generator Gs generates as well a series of advance pulses for the scanning devices; these pulses are available on line La and may, for example, be negative as those shown in the time diagram.

Line La is wired to an input of logical "OR" circuits OTA and OTB (FIG. 4h). The right and left outputs of trigger TAB are respectively wired to the second input of OTA and OTB; the output pulses OTA and OTB make up advance pulses A and B. These pulses are available on lines T'A and T'B and are shown on the time diagram (FIG. 13). These advance pulses T'A and T'B are applied to the fast input of diode gates PAB and P'AB and are used to switch trigger TAB on or off in order to determine the limits of time intervals A and B.

Advance pulses A cause the progression of scanning device A, i.e., switches the "on" trigger of device A "off and switches the following trigger "on" so that the triggers of device A are successively held on, first during a time B, then during the following time A. The same happens for advance pulses B and scanning device B, as shown in the time diagram (FIG. 13) in which trigger n of scanning device B remains on during a time A, then during the following time B, trigger (n-1) being on during both times A and B, which follow.

Obviously, other timing arrangements might be used, such as, for example, the one shown in the time diagram (marked "Alternate Operation" in FIG. 13), according to which the on time of trigger n of scanning device B would first include a time B, then the following time A.

In FIG. 4i, all the storage groups have been marked with M and represented symbolically by a dotted line square, in which appear the 7 magnetic cores N1, N2, N4, N8, NA" NB and NC of a single position, for example, position 12 of storage group H2. It is quite obvious that all the positions of all the storage groups might be identical. When tens trigger D'1 and unit trigger U'2 of scanning device B are on, they determine position 12 of selected storage group M2, i.e., during B time the signals on the right output of D'1 and U'2 go through 75 logical "AND" circuits Ep, logical "OR" circuits Op

and favor an input of logical "AND" circuits EL and E'L (FIG. 4h) (the other input of which is favored, during the reading times, by a signal proceeding through line LL); they energize current pulse generators or core drivers GL and G'L and generate, during reading times B, magnetic fields

$-\frac{H}{2}$

and

$$-\frac{H}{5}$$

in the sense windings of the 7 cores of position 12; these magnetic fields do not modifiy the remanent state of the cores which were in state 0; on the contrary, they switch back to state 0 the cores which were in state 1, by generating an output signal on corresponding lines L'1, L'2, L'4, L'8, L'A', L'B or L'C. Then, during the recording times, the pulse from line Le favors an input of logical "AND" circuits Ee and E'e; the signals on the right output of D'1 and U'2 go through Ep, Op and Ee or E'e energize current pulse generators or core drivers Ge and G'e, and generate magnetic fields

$$\frac{H}{2} + \frac{H}{2} = H$$

in the record windings of the 7 cores. The recording takes place in a core, i.e., its change from remanent state 0 to state 1 occurs only for those among the 7 cores in which an inhibiting magnetic field

$$-\frac{H}{2}$$

is not generated simultaneously. The inhibiting current pulse generators or inhibition core drivers have been symbolically represented with squares marked G1, G2, G4, G8, GA, GB and GC (FIG. 4i).

It is quite obvious that this operation, described as mere indication, may be adapted to any other type of magnetic cores, to other information recording or reading methods, or pulse generators operating according to other principles. For example, other methods would relate to using: (1) core drivers GL and Ge (reading and recording) which generate current pulses of same direction, in opposite direction windings to apply successively, to the magnetic core, opposite magnetic fields -H, reading, and +H, recording; (2) core drivers producing in the same windings current pulses of opposite direction; (3) a limited number of core drivers, each for supplying in common the cores of several positions, and several switches controlled by the scanning devices so that, when a position is reached by the scanning device, the corresponding switch make and the core driver generate the magnetic field in the 7 cores of this position. The core drivers and the switches may be of any type, for example, of the tube or transistor type, or made up of a magnetic core matrix.

# Transfer With Redistribution (FIGS. 4h, 4p, 4q and 4r)

In a general manner, in the working storage, the information is not arranged the way it should be printed or punched. In this case, the transfer of the information contained in field A, toward field B or output storage, must occur together with a redistribution. The line is edited in series, the data are accumulated in order in the successive positions, the storage field determined by chain B covers all the positions of the line to be edited, i.e., the scanning of field B is continuously performed from the extreme right position up to the last position left of the output storage.

Each time, and it is the general case, when, during the programs preceding the print edit, it was not possible to join together the words which are to be read out of the working storage, in order to enter them into the out-

16

put storage, scanning device A, which determines the outgoing quantities, must be conditioned by scanning device B which scans the area in which the line is being composed.

The conditioning of a chain to the other is described in our copending application Serial No. 643,369, filed Mar. 1, 1957. This conditioning enables the scanning chain A to perform skips controlled by chain B. It means that both chains A and B progress normally, until in chain 10 B a determined stage, for example 40, is switched on. Then the output signal of triggers D'3 and U'10 of chain B controls the stopping of chain A and its restart from any stage, for example 71. For this, it is sufficient to wire output terminal 40' of chain B (output of both D'3 and U'10 triggers) to input terminal 71 which is common to both chains A and B; see dotted line connection in FIGS. 2a, 2b and 2c (and FIGS. 4p, 4q and 4r). The stage 71 selected for this connection will be the one which determines the position on the extreme right of the new storage to be transferred.

In case the new field to be transferred is not in the same storage group, the chain A skip control must occur together with a group change control. For this (see FIGS. 2a, 2b and 2c), the control pulse emitted for example by output terminal 10' of triggers D'o and U'10 of chain B is applied through a circuit C12 which permits the feeding of two pulse receiving terminals, one of them 31 used as previously to determine the storage position, while the other defines the new storage group.

Between the moment when chain A is stopped and the one when it starts again from the new position, the progression of chain B stops for a while and the transfer of the information contained in the last position determined by chain A is not transferred in field B. Then, both chains progress normally and the information transfer resumes as previously described, unless the information redistribution requires a new skip control.

The skip device comprises essentially 3 skip triggers BI, BII and BIII logical "OR" circuit SO and logical

"AND" circuit Se (FIGS. 4h, 4p, 4q and 4r).

No matter which input terminal of the scanning devices is energized by the skip control, a signal is applied to one of the 8 inputs (which corresponds to the 8 series of ten) of logical "OR" circuit So, and goes through it. It is the signal on the output of So which allows the detection of a skip control and which switches the skip device on. For this, it is applied to an input of logical "AND" circuit Se. The 3 other inputs of Se are favored when the 3 following conditions are met:

- (1) The control program is "print edit" or "punch edit," a signal proceeding from terminal CI or CP through logical "OR" circuit OIP (FIG. 4c).

- (2) The skip device is not on, a signal proceeding from the left output of skip trigger BII (FIG. 4h).

- (3) The start control has already occurred.

The signal on the output of Se is applied on the slow input of diode gate PI; the first advance pulse A applied through line T'A to the fast input of PI switches skip trigger BI "on." The right output of BI is wired to the slow input of diode gate P'I; the first advance pulse B, applied through T'B to the fast input of P'I resets trigger BI and switches trigger BII on. The right output of BII is wired to the slow input of diode gate P'II; the following advance pulse B applied through line T'B to the fast input of P'II switches trigger BIII on and BII off. The output of BIII is wired to the slow input of diode gate P'III and the following advance pulse B switches trigger BIII off. The three triggers BI, BII and BIII are now off and the skip device is back in its original state ready to respond to a new skip control.

As a conclusion, when a skip is controlled, the three triggers BI, BII and BIII are switched successively on; they are switched off when the following one is switched on. The "on" times of the three triggers BI, BII and BIII are shown in the time diagram (FIG. 13).

The main purpose of these three triggers is:

(1) To reset scanning device A; for this, to switch off the "on" triggers.

(2) To stop the progression of scanning device B; for this, it is sufficient to eliminate advance pulses B until scanning device A is relocated.

(3) To restart scanning device A from the stage determined by the established connection (stage 71 according to the given example, the dotted line connection shown in FIGS. 4p, 4q and 4r). In order to switch tens trigger D7 and units trigger U1 of scanning device A, the signal on the right output of trigger BI goes through logical "OR" circuit Od and allows, through line Ld, the application of a start pulse to all logical "AND" circuits ed, the second input of circuits ed corresponding to a series of tens 7 and to units 1 being favored by input terminal 71.

(4) The information proceeding from the last position reached by scanning device A must not be transferred in field B of storage; for this, the read pulses are eliminated when trigger BI is "on."

Skip triggers BI and BII directly operate on timing generator Gs in order to obtain an additional advance pulse for scanning device A, or to eliminate an advance pulse for scanning device B. This operation is explained in detail in copending application Serial No. 643,369. 25 During the "on" time of trigger BII which includes a time A and a time B, the information from the new position A is transferred in storage position B.

Other information proceeding from another control could also be recorded in the position in which the skip 30 is controlled, for example, an insertion of symbol "—," minus. The other purposes of these three triggers BI, BII and BIII and more particularly those which allow simultaneously control of a skip and another function from the same output terminal of the scanning device 35 will be described in the corresponding chapter.

# Insertion of Characters

All the letters, digits and special characters such as, for example, & . \$ , / , %, etc., may be inserted in the 40 line to be composed, in any position as desired by the operator. To each one of these characters, corresponds a terminal marked A, B, C, D, E . . . X, Y and Z, 1, 2, 3, 4 . . . 8, 9, 0, b (blank) . \$ & @ %, etc. (FIGS. 4n and 4w).

It is possible to insert either a single character or several successive characters in order to make up a word, TOTAL, for example, or a group of words.

The insertion of a character may be conditional or not. For example, the insertion of sign "—" may be 50 controlled unconditionally or the operator may wish that sign "—" be printed only if the quantity is negative; in this case, it is the machine which detects the sign of the quantity and determines whether the sign "—" must be inserted or not.

The position in which this insertion takes place may be either determined in advance or depend upon the quantity. For example, the doller \$ character may be inserted in a fixed position or on the left of the high order significant digit of the quantity.

At this point, only the unconditional insertions in determined positions will be described, the others will be described hereinbelow.

The insertion relates, during the transfer of a storage field A to a B field, to stopping this transfer during as many cycles as there are characters to be inserted and to record in field B the desired characters. Consequently, the insertion of a character stops the progression of scanning chains A, while preventing the reset of the register which keeps the information read in the last position reached by chains A so that after the insertions, the information kept in the register be recorded in field B. Then chain A resumes its progression and the transfer goes on until a new exception, eventually wired. These functions will be performed as well if the insertion

is controlled by the wired connection as if the insertion occurs automatically, i.e., is controlled by one of the devices described in further chapters, and which allow such operations as "floating dollar," CR insertion, etc.

In order to insert a character, Z for example, in a position such as position x of the storage, it is sufficient to connect with a flexible wiring the output terminal of the stage x triggers of scanning device B to the terminal corresponding to the selected character Z. The output terminals of scanning chain B are pulse emitters, the terminals corresponding to the characters to be inserted are pulse receivers; consequently, it is possible to wire one same "characters" terminal to two or more different terminals of chain B. These connections will allow the same character to be inserted into various positions of the line.

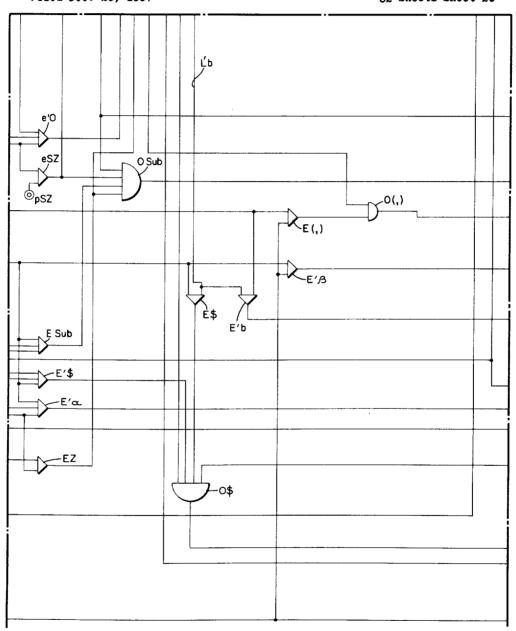

When the started program is a print or punch edit operation, scanning chain B starts from the extreme right position of the line to be composed and once started, it progresses toward the left from position to position and scans the storage up to the end of the line. Hence, all the output terminals of all the stages of chain B will emit successively synchronized pulses upon the scanning of the storage corresponding position. When scanning chain B reached position x of the storage, the pulse emitted by the chain will travel from the terminal corresponding to stage x to the terminal marked Z. This pulse goes through logical "OR" circuits OA and O18, then O'A, O'1 and O'8 (FIGS. 40 and 4x), letter Z being translated in the storage by bits 1, 8 and A. The output signals from O'A, O'1 and O'8 go through logical "AND" circuits eA, e1 and e8, the second input of which is favored through logical "AND" circuit EI; as a matter of fact, a signal appears on the output of EI, if, during a time B, the two following conditions are met together:

(1) There is no blank to be inserted. As a matter of fact, as it will be explained in the blank insertion chapter, a blank to be inserted has priority on the control of any other function. The corresponding signal proceeds from the left output of blank insertion trigger Bb (FIG. 4m).

(2) A "print edit" or "punch edit" program has been controlled from terminals CI or CP through logical "OR" circuit OIP (FIG. 4c).

In order to record a Z in position x, among the 7 cores of the storage position x, cores 1, 8 and A must switch from remnant state 0 to state 1. Starting from the output of logical "AND" circuits e1, e8 and eA, bits 1, 8 and A, corresponding to letter Z to be inserted in position x of the storage area B, go on exactly as if it were the transfer of letter Z from the register toward position x; this means that signals 1, 8 and A proceeding from "AND" circuits e1, e8 and eA go through logical "OR" circuits O1, O8 and OA, and are applied to the input of inverters II, I8 and IA (FIGS. 40 and 4x). A signal appears only on the output of inverters 12, 14, IB and IC; corresponding inhibition current pulse generators G2, G4, GB and GC (FIG. 4i) apply to the windings of the cores corresponding to bits 2, 4, B and C an inhibiting magnetic field

$$\mathbf{-}_{\mathbf{2}}^{H}$$

at the same time, the tens and unit triggers of scanning 5 chain B allow to generate fields

$$+\frac{H}{2}+\frac{H}{2}$$

in the 7 cores of the storage position x. As a conclusion, cores 1, 8 and A of position x switch to saturation state 1; letter Z has been inserted.

the information kept in the register be recorded in field B. Then chain A resumes its progression and the transfer goes on until a new exception, eventually wired. These functions will be performed as well if the insertion 75 Unring the cycles preceding this cycle x of chain B, scanning chain A has reached a position of field A of the storage; as during a normal transfer, the information read in this position of field A has been written in the

7 trigger register, then regenerated in the same position of field A. However, when chain B reaches position x of the storage, the signals corresponding to the bits to be inserted must be recorded, in this case 1, 8 and A; they go through logical "AND" circuits e1, e8 and eA 5 then logical "OR" circuit OI (FIG. 40), the 7 inputs of which are wired to the outputs of the 7 logical "AND" circuits e1, e2, e4, e8, eA, eB and eC. Consequently, there will be a signal on the output of OI no matter what the character to be inserted is, i.e., no matter what 10 the bits to be recorded in the storage are, even if there is a single bit to be recorded, for example, if it is desired to insert digit 8 which is represented by single bit 8.

The signal on the output of logical "OR" circuit OI performs two functions:

(1) It prevents the information written in the 7 trigger register, and which has just been read out of field A, from being recorded in position x of the storage.

(2) It switches hold trigger Bm, on in order to stop the progression of scanning chain A, by eliminating the 20 advance pulses of this chain, and prevents the resetting of triggers B1, B2, B4, B8, BA, BB and BC of the register, in order to keep in it, the information to be recorded, when the insertions are over.

(1) The signal on the output of logical "OR" circuit 25 OI is applied to the input of inverter II (FIG. 4g). The output of II is wired to an input of logical "AND" circuit E'I, the second input of which is favored during time B. If there is a character to be inserted, there is a signal on the input of II, there is no signal on the output of II, hence no signal on the output of E'I nor to that of logical "OR" circuit e'I; and an input of logical "AND" circuit e'I; and an input of logical "AND" circuits E'1, E'2, E'4, E'8, E'A, E'B and E'C (FIG. 4g) is not favored any longer. Consequently, during times B, the signals from registers B1, B2, B4, B8, BA, BB and BC may no longer be recorded in position x of the storage, since lines L1, L2, L4, L8, LA, LB and LC are interrupted.

In position x of the storage, the character to be inserted is recorded, while the information proceeding from the register may not be recorded any longer. On the contrary, if there were no character to be inserted, there would have been no signal on the output of OI, nor on the input of inverter II, but then, there would have been 45 a signal on the output of II; this signal would have gone through "AND" circuit E'I and "OR" circuit O'I in order to be applied to an input of logical "AND" circuit eI. The second input of eI is favored when the current program is a transfer, a print or punch edit; 50 as a matter of fact, through the control wiring of this program a pulse is applied to one of input terminals Tr, CI or CP respectively transfer, print edit and punch edit. When one of these two last programs is controlled, there is a signal on the output of "OR" circuit OIP (FIG. 55 4c) and when one of the three is controlled, there is a signal on the output of "OR" circuit OTC, and it is this signal which favors the second input of el. The third input of eI is wired to the output of inverter IR (FIG. 40) for resetting the output storage; this input is favored when no signal is applied to the input of IR, i.e., as long as the line composition is lasting. Inverter IR will be described in chapter "output storage reset." output signal from eI favors logical "AND" circuits E'1, E'2, E'4, E'8, E'A, E'B and E'C which consequently allow, during time B, the recording in field B of the information from the register.

During time A, when the controlled program is a transfer or an editing, an input of "AND" circuits E'1, E'2, E'4, E'8, E'A, E'B and E'C is favored, in a similar way, by the signal which exists during time A, which is through line TA applied to the second input of "OR" circuit O'I and which successively goes through O'I and then "AND" circuit eI.

As a conclusion, the information read in a position of field A of the storage and written in the register is always rerecorded in the same position of field A, while its transfer toward a position of field B is allowed only if there is no character to be inserted. But, immediately after the insertion of the character or characters is over, the information transfer from field A to field B, interrupted during the insertion, resumes, beginning with the recording in B of the last information read in A; but to perform this function, this information is to be kept in the register.

(2) Duty of hold trigger Bm (FIG. 4g): A signal appears on the output of logical "OR" circuit OI (FIG. 40) only if there is a character to be inserted; this signal is applied to an input of logical "AND" circuit Em. Circuit Em receives three other signals, a first signal which exists only during the forward scanning of the storage and does not exist during the backward scanning, since during backward scanning, substitutions may occur, but no insertions (through line L'd this first signal proceeds from the output of inverter I'd (FIG. 41), the input of which receives during the backward scanning a signal applied by line Li); a second signal which does not appear for the positions in which a skip has been controlled, which proceeds from the left output of skip trigger BI (FIG. 4h) and which appears for all the positions in which no skip has been controlled in order to avoid any confusion between skip and insertion control; finally a third signal which exists only if no substitution has been controlled. This third signal proceeds from ineverter Isub output (FIG. 4n), the input of which is wired to logical "OR" circuit Osub output (FIG. 4u).

The four possible cases of character substitution are grouped on the four inputs of this circuit Osub, they will be considered in the following chapter. If there is a substitution of character to be performed, there will be a signal on the output of Osub and no signal on the output of Isub; "AND" circuit Em will not be favored. On the other hand, if there is no substitution to be performed, there will be no signal on the output of Osub hence a signal on the output of Isub which will favor the corresponding input of Em. Consequently, a signal will appear on the output of Em if, during the forward scanning and in the absence of a skip control, there is an insertion and no substitution to be performed; this signal favors the slow input of diode gate Pm. A pulse proceeding from the timing generator Gs and applied to the fast input of Pm switches hold trigger Bm on (FIG. 4g). Trigger Bm is reset through diode gate P'm the slow input of which is favored, in the absence of skip control, by the signal from the left output of skip trigger BIII, and the fast input of which, wired through line T'A to the output of logical "OR" circuit OTA (FIG. 4h) receives the progression pulses of scanning device A (see time diagram, FIG. 13). Trigger Bm is switched back on during each one of the insertions to be performed. As soon as there is no more insertion to be performed, none of the 7 inputs of OI receives any signal; there is no signal on the output of Em, diode gate Pm is not favored any longer, hold trigger Bm no longer switches "on" but remain "off."

Trigger Bm is on while chain B scans the positions in which an insertion is controlled, in the selected example, position x of the storage. A signal is available on the left output of Bm only if Bm is off; this signal favors an input of logical "AND" circuit E'm (FIG. 4b). The other inputs of E'm are favored during time B, through line TB; during the absence of skip control by the signal on the left output of skip trigger BII and by the output signal of "OR" circuit OTC (FIG. 4b), when the controlled program is a transfer, or print or punch edit.

The signal on the output of E'm favors the slow input of the 7 diode gates P1, P2, P3, P4, PA, PB and PC (FIG. 4j); their outputs, wired to the left inputs of regis75 ter triggers B1, B2, B4, B8, BA, BB and BC allow to