#### ENGINEERING DESCRIPTION OF EXPANDED CALCULATE

II Divide:

## A Introduction

In any divide operation, the location of the high order quotient position must first be found. This is done by starting at the high order position of the quotient field (fig. 1-a) and counting toward the low order a number of digits equal to the number of significant digits (fig. 1-b) in the divisor. The divisor- of length N significant digits- is then compared to the N high order positions of the dividend (fig. 1-c). If the divisor is larger than the "partial dividend", the first quotient digit is zero. and the divisor is then compared to the (N+1) positions of the dividend, (fig. 1-d). When a partial dividend which is greater than the divisor is found, the divisor is subtracted from the partial dividend until the partial dividend becomes smaller than the divisor. The number of subtractions made determines the magnitude of the quotient digit (fig. 1-e) corresponding to this particular partial dividend. The number of significant digits in the quotient may be increased by adding zeros to the low order positions of the dividend field (fig. 2).

This basic procedure is used in the expanded calculate option of the 1401. However, if the magnitude of the partial dividend is at least twice the magnitude of the divisor, the divisor is doubled before being subtracted from the partial dividend, and the corresponding quotient dight is increased by two.

The locations of the various fields are shown on page IV and are referred to in the explanation which follows:

### B Procedure

Prior to giving the divide instruction, an area must be provided in storage for the quotient and dividend. This area consists of a dividend field located anywhere, and a quotient field of the same length as the dividend field, but immediately to the "let" of the dividend field, but immediately to the "let" of the dividend field in storage (fig. 3). The number of significant

digits in the quotient may be increased by lengthening the dividend field with zeros in the low order positions, thus increasing the length of the quotient, (fig %). In this case, the programmer must keep track of the decimal point.

Your Marken must be placed in storage to denote the high order positions of both the quantism and dividend fitsids. Then the dividend must be pliked in the dividend fitsid by either a "nove", "lead", "reset-subdy". Also, the dividend must carry a sign (B bit only for "minus", both A and B bits for "plus") in tits 'units positions, and there may be no other B bits for the property of the plus of the

The divisor field may be located anywhere, but may not be greater than the length of the dividend field, and must have a sign (8 bit only for "minus", both A and B bits for "plus") in its' units position. No other B bits may be located in the divisor field.

When all of the above conditions have been satisfied, the "Divide" instruction may be given. This is a two address instruction:

## % (AAA)(BBB)

where (AAA) must be the address of the divisor field and (BBB) is the

This instruction first locates the high order quotient position and indicates this condition by inserting the proper sign bile into the quotient field. The high order significant digit of the divisor to then aligned with the high order position of the division and the divisor may be compared to the dividend. The divisor will then be subtreated from the dividend a number of itse depending upon the results of this comparison, and the results of this comparison, and the results of the comparison, and the dividend dependence smaller than the divisor, the quotient sign will be altifed to the next lower order position and the partial dividend will be extended by increasing the address of itsel low order digit, until another subtraction can be sude. At the conclusion of the another subtraction can be sude. At the conclusion of the another subtraction can be sude. At the conclusion of the another subtraction can be sude.

Two additional address registers are required for this option: the A auxiliary address register and the B auxiliary address register. The A suxiliary address register always holds the address of the units position of the divisor as that whenever the divisor is to be compared to, or subtracted from, the dividend, the A address, register may be returned to its' starting point by effecting a transfer of the contents of the A suxiliary address register to the A address recister.

The B suxiliary address register holds the address of the storage location of the units position of the "partial dividend" to which the divisor is being compared and from which the divisor is being subtracted. The address is increased by "1" whenever the partial dividend is found to be smaller than the divisor. This address change, in turn, causes "shift" in the addressing of the dividend field. The contents of the B auxiliary address register to the proper starting point each time the partial dividend is to be compared to the divisor or the others as subtracted divisor is subtracted.

## The detailed operation is as follows:

When the Divide Op code (%) is detected in the B register, the A auxiliary address register is gated to receive the A address as is the A address register; then the B auxiliary address register is gated to receive the B address as is the B address register.

The quotient field must first be set to zero, the high order quotient position must be located, and the divisor and dividend must be properly aligned so that they may be commared.

## This is accomplished in the following way:

A and B cycles are taken until the word mark in the divisor field is detected. (During the first two cycles, the divisor and dividend signs are analyzed, and the proper quotient sign is stored in a trigger.) B cycles only are then taken until the word mark in the dividend field is detected. This word mark signifies the end are then read into a trigger. In the contract the contrac

digit of the divisor are about to be addressed. B and A cycles are taken in the reverse direction until the B bit in the units position of the divisor is detected, causing the elimination of succeeding A cycles. During the following B cycle, the proper quotient sign is h inserted into the quotient field. This sign indicates the position of the first quotient digit. The next step is to align the high order significant digit of the divisor with the high order position of the dividendum This is done by first continuing B cycles until the word mark in the high order position of the dividend field is detected. A cycles are now taken in the forward direction until the word mark in the high order position of the divisor field is detected. The detection of this word mark starts a reverse soan of the A (divisor) field and A cycles continue until the first significant digit of the divisor field is sensed. At this point, the high order position of the dividend field and the first significant digit of the divisor are about to be addressed. Now B and A cycles are taken until the B bit in the units position of the divisor is detected. The address of the low order position of the first partial dividend is read into the B auxiliary address register during the final B cycle of the alignment of the divisor and dividend fields. and the divide operation proper may begin.

A and B cycles are taken in the forward direction to compare the divisor (of length N digits) to the first "N" digits in the high order positions of the dividend. He-yeles only are then taken in the forward direction until the sign bit in the quotient field is detected.

There are five possible results of this commarison:

- a) Twice divisor < partial dividend

- b) Twice divisor = partial dividend

c) Divisor < partial dividend < twice divisor

- d) Divisor = partial dividend

- e) Divisor > partial dividend

The following action, based upon the results of this comparison, then takes place.

## a) Twice divisor < partial dividend

A B-cycle is taken to increase the quotient by two, The quotient sign does not change location. A and B-cycles are taken to subtract twice the divisor from the partial dividend and compare the divisor to the reduced partial dividend. (See Appendix) When a word mark is detected, B cycles only are taken until the B bit in the quotient field is detected. b) Twice divisor = partial dividend

Same as (a). In this case, after subtraction, the partial dividend will be reduced to zero.

c) Divisor < partial dividend < twice divisor

Two B cycles are taken in the rewerse direction to increase the quotient by Tope, and shift the quotient sign to the rant lower cords; provided the continue of the continue of the continue of the subtract the direction of the continue of this subtraction, the partial dividend is extended to the next lower order position, by partial dividend is extended to the next lower order position, by correasing the address in the B auxiliary address register. A normal comparison of the divisor with the new partial dividend is now made.

d) Divisor = partial dividend

Same as (c). In this case, after subtraction, the partial dividend will be reduced to zero.

e) Divisor> partial dividend

Three B cycles are taken in the reverse direction. During the first B cycle, the quotient sign is read out of storage, During the second B cycle, the sign is read to the storage, causing a shiff in the quotient to the mext lower order position. During the third B cycle, the address in the B auxiliary address register is increased by one, causing a "shift" to the next lower order position in the partial dividend. The reverse scan is stopped, and a normal comparison of the divisor with the new partial dividend is made.

The divide process is terminated, and an I/S change is forced when the sign in the units position of the dividend is detected, and a comparison which shows that the dividend is also than the land of the sign of

John Bakoski John Pokoski Department 260

#### APPENDIX

Whenever a subtraction of the divisor from the partial dividend is performed, a simultaneous comparison of the divisor with the new partial dividend is made.

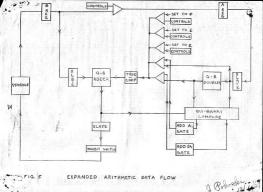

Figure 5 shows the data-flow path from storage into the adder.

A previous comparison has determined whether the divisor or twice the divisor is to be subtracted from the partial dividend.

If the divisor is to be subtracted from the partial dividend, an Acycle is taken during which the divisor digit is moved from atomage, through the B register, and into the A register. It is then translated into qui-thong roots and gated through the true complement circuitry and into the adder. The output of the true that the complement circuitry and into the adder. The outbut of the guideline of the complement of the complement circuitry to the control of the control

The same paths are followed if twice the divisor is to be subtracted from the partial dividend except that the divisor digit is doubled before being complemented and read into the adder.

During the following B cycle, the partial dividend digit moves directly into the B register, is immediated to qui-binary, and ensize the second of the second of the second of the second of the second into the adder. A complement addition is performed so that either the divisor digit for their the divisor digit is subtracted from the partial dividend digit. This operation is completed by 7.5 time of the cycle. At this time, the output of the adder is gated into compare circuitry so that the reduced partial dividend digit is commared to the divisor digit and twice the divisor digit;

Although the divisor and twice the divisor are being compared to the reduced partial divided during all subtractions, the results of the results of the compared partial divided during all subtractions are considered as the compared of the compared to the compared of the compared to the compared of the

The "set to 1" and "set to 2" gates shown in figure 5 are used to gate either the digit "1" or the digit "2" through the true complement circuitry and into the adder so that the quotient digit may be increased by either "1" or "2", as determined by the previous divisor-partial dividend comparison.

The "set to 0" gate is used to force a zero into the adder when first aligning the divisor and dividend so that the digit in the B register will not be added to the digit in the A register before being gated out of the adder and into the compare circuitry. This gate is also up immediately after the partial dividend address is "antired", so that a new comparison can be . co: Messre. O. R. Ahearn

F. W. Baldwin G. E. Beers

A. A. Bissell

R. L. Bennett S. Bespalko

E. M. Bloom G. E. Bontecou

N. C. Capettini

B. N. Carr J. S. Conzola

P. Farbanish

J. O. Fitzgerald E. J. Grenchus

J. A. Harvilchuck J. J. Ingram

P. E. Johnson

W. L. Kelly R. W. Phillips

T. Markalin T. M. McAdon

F. M. McAdon

W. K. Rings

T. H. Rowe

R. A. Rowley B. T. Rucker

W. S. Schaffer K. B. Stoffel

K. B. Stoffel

F. O. Underwood

W. J. Zehner

a) High order quotient position

b) Divisor (of three significant digits)

c) First partial dividend d) Second partial dividend

e) Quotient digit (determined by number of subtractions made)

Remainder

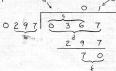

fig. 2 0297 036700 -0297 700 -594 1060

-0594 466 -291

## Quotient field Dividend field

8-field | 096 | 096 | 091 | 098 | 099 | 100 | 010 | 028 | 099 | 090 | 010 | 028 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 039 | 03

fig.3

# Quotient field Dividend field

| 090 | 091 | 091 | 095 | 094 | 095 | 096 |     | 6  |   |   |   |

|-----|-----|-----|-----|-----|-----|-----|-----|----|---|---|---|

| *   | _   | -   | -   | _   | -   | 1   | 212 |    |   |   |   |

|     |     |     |     |     |     |     |     | Q. | 2 | 9 | 7 |

fig.4