February 2, 1961

MEMORANDUM TO: Mr. B. Q. Evan

SUBJECT:

Study of 16K-64K Storage for Stage III 1401

# I Statement of the Problem

The purpose of this study was to propose and evaluate a method for expanding to 64K the maximum storage presently planned for the Reduced Cost 1401. This engineering proposal was to be evaluated by Applied Programming also to determine effects on existing and proposed 1401 programs.

To define the problem further, Measrs. J. H. Frame (Applied Programming), G. R. Ahearn and L. E. Farr (1401 Engineering), agreed that any proposal should:

- Provide maximum compatibility with programs written for Stage II 1401 systems.

- 2. Include indexing facilities.

# II Surmary of Results

Additional Storage

Estimated Base Product Cost

16K 8,050 - 9,850 32K 14,300 - 17,400 48K 20,500 - 26,000

Costs are based on mounting additional arrays, memory circuits and power supplies in a separate frame.

By way of comparison, the difference in product cost between a 1401 Model 3 (4K storage) and a Model 6 (16K storage) is \$4,851 with a corresponding rental difference of \$1,650. A rough estimate by Marketing indicates that there might be a demand for 35 to 60 systems with more than 16K of storage.

Schedules would be extended an estimated 6 months should this proposal be incorporated in the present development program for the Stage III 1901. Additional manpower would be required also (estimate minimum need for three engineers and two technicians for 6 months)

## III Logic Approach

### 1. General Description

The existing address structure has the capacity for 64,000 combinations of the index tag bits are carried in another combinations of the index tag bits are carried on another carried over the examinate A, B and C some bits would be carried over the carried over

The system with 64,000 characters of storage will be capable of running programs with either; sharacter or 8 character addresses. It would be required that the type of program to routine. In addition, it would be possible to change program mode during the operation by say of a special instruction. The program of the pro

Now that an entire character is allocated to the index tag, it is certainly possible to have more than 3 index register words.

## 2. Detailed Description

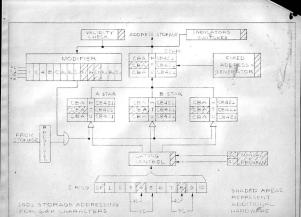

The Address Register section must be expanded to handle 3 additional bits in each of the 4 registers. In a Multiply Divide system the A auxiliary register and the B auxiliary register would each require the 3 additional bits.

The Instruction Ring must have the ability to expand two extra positions. This expansion is a function of the type program and is controlled accordingly.

The Program Mode Latch would indicate the 4 character program if it were set, and the 3 character program if it were reset. Provision is made to set the latch by way of a Duit Op code followed by a modifier, or by way of a manual pushbutton.

Frotision to reset the latch would be by may of a Unit Opode with another modifier, by a pushwithou on by the load key. Note that when programs enter the machine as a result for a superior of the program of the catch would propare the system for 3 charpy the program of the program of the program of the programs must be 3 character node. This situation is desirable because it would be a simple matter to insert a Node Charge insignition (Unit Op followed by modifier) within the that the declaracter material to followables the controls for the 4 character material to follow abilish the controls for

The addressing Validity check and modifier must be expanded to accommodate the additional zone bits over the tens digit. The circuitry in the Fixed Address Generator must expand to cover the 3 extra bits.

The following additions must be made to the indexing section if it appears on the machine:

- a) Provide 3 extra lines in the path from the stars to the "A" register.

- Provide alternate means of setting the Index tag latches under control of the Program Mode Latch.

- e) Provide a conditional arithmetic cycle in the event of a carry out of the units zone bits.

The circuitry associated with the Address Modify instruction must be reworked to provide for an additional cycle in the event of a carry out of the units zone addition.

The Address Stop circuitry must be expanded to make the comparison on the 3 extra bits.

The fact that the additional circuitry is remotely located, necessitates extra signal drive blocks.

Logic has been detailed beyond that shown in the attached flow diagram to obtain approximate card counts. No detailed consideration has been given, however, to providing more index registers.

-3-

The addressing Validity check and modifier must be expanded to accommodate the additional zone bits over the tens digit. The circuitry in the Fixed Address Generator must expand to

cover the 3 extra bits.

The following additions must be made to the indexing section if it appears on the machine:

- a) Provide 3 extra lines in the path from the stars to the "A" register.

- Provide alternate means of setting the Index tag latches under control of the Program Mode Latch,

- c) Provide a conditional arithmetic cycle in the event of a carry out of the units zone bits.

The circuitry associated with the Address Modify instruction must be reworked to provide for an additional cycle in the

The Address Stop circuitry must be expanded to make the comparison on the 3 extra bits.

event of a carry out of the units zone addition.

The fact that the additional circuitry is remotely located, necessitates extra signal drive blocks.

Logic has been detailed beyond that shown in the attached flow diagram to obtain approximate card counts. No detailed consideration has been given, however, to providing more index registers.

## IV. Storage Implementation

#### A. Arrays and Circuits

To provide a total of 64K of storage, 3 sections of 16K each have been assumed in addition to the basic 16K section. Each section has its own drivers and sense amplifiers. All this additional Bromage hardware would be in a separate frame which is tied to a system like the present 140K.

The 16% storage for Stage II 1801 systems is packaged in three sections of 2.8 Ga and AE. Rach section has 12 spond relevant control of the c

#### B. Hardware

The three 16% arrays and associated circuits must be mounted in a separate double frame, in a saners similar to the present 1400 attachment. Additional power supplies must be provided for these circuits and sequencing circuits to control them. In the sature frame, but one intending classes would be needed in this extra frame, but one intending the mounted in this extra frame, but one intending the mounted in this extra frame, but one intending the mounted frame that call th

The main (JEM) frame would require modifications in several areas. The sale entry is already cruedes without allowances for more storage. At the moment, this appears to be a severe for more storage. At the moment, this appears to be a severe possible special construction of the sale of the sal

Product costs on all these items are tabulated in Appendex I. It may be desirable to provide two models of certain CPU chassis in order to expand CPU logic for large memory aystems without adding costs to small system. Cost figures do not include amounts for this arrangement.

# V Programming

Programs presently written for Stage II 1401 systems will be completely compatible with GAR memory systems. New programs must be writtened or companies to utilize the added memory and these programs and the companies of the stage of the companies of the communication links to old programs with which they may be intermined.

-5-

Programming costs to utilise GAK of storage, therefore, are the costs of compiling new programs specifying addresses above 16X. There would not program specifying addresses above since they would not be supported to the programs, as time they would not be supported to the programs.

The above statements are based on the limited investigation which has been possible during the one week spent on this overall proposal for expanding Stage III 1401 storage capacity

O. R. Ahearn

V. E. Fan.

L. E. Parr

9. L. Pokoski

cc: Mr. G. R. Baskin Mr. J. H. Frame

Mr. J. A. McDonnell Mr. P. O. Underwood

## Appendix I

These product cost estimates are of limited accuracy. They indicate "ballpark" figures only.

# Added CPU Costs

THEO, I

Item Estimated Base Product Cost

Additional 16K 1,150 - 1,550 Additional 32K 1,200 - 1,600 1,200 - 1,600

# Additional Frame, Arrays, Power Supplies, Chassis

Additional 16K 6,900 - 8,300 Additional 32K 13,100 - 15,800 Additional 48K 19,300 - 24,800